基于DSP的数字图像处理系统中的抗干扰设计方案

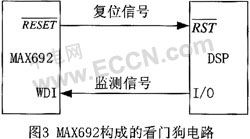

掉电判别、看门狗监控等功能。其中WDI是看门狗检测输入端,接到DSP的一个专用I/O口或一个总线口上。是复位信号输出端,接DSP的复位端。MAX692的WDI定时周期为1.6s,复位脉冲宽度是200ms。如果WDI保持高或低超过"看门狗"定时周期(1.6s),端将发生200ms宽(最小140ms)的负脉冲使DSP复位。

2.3 软件抗干扰技术

利用软件也可以提高DSP数字图像处理系统的抗干扰能力。主要有:①利用数字滤波器来滤除干扰;②采用软件看门狗、多次采样技术、定时刷新输出口等技术来抑制干扰。下面主要介绍数字滤波器在本系统中的应用。

数字滤波器(DF)对图像信号的处理过程如图4所示。图像信号首先经过采样/保持电路(S/H),送至模/数转换器(ADC)转换成数字量,然后通过数字滤波器滤除其中的干扰信号,最后通过数/模转换器(DAC)获得语音信号输出。

根据所用数学模型的不同,数字滤波器可分为两大类:一类是递归型滤波器,其特点是滤波器的输出不仅与输入信号有关,还与过去的输出值有关;另一类是非递归型滤波器(如一阶、二阶低通滤波器),其特征是滤波器的输出仅与输入信号有关,而与过去的输出值无关。本系统中使用的是递归型滤波器。

数字滤波器的软件设计方法有:程序判断滤波法(限幅滤波法)、中位值滤波法、算术平均滤波法、递推平均滤波法、防脉冲干扰平均滤波法、一阶滞后滤波法等6种方法。根据需要,本系统选择中位值滤波法。

设数字滤波器的输入信号为一个一维序列?l,?2,…,?n,取窗口长度(点数)为m (m为奇数),对其进行中位值滤波,就是从输入序列中相继抽出m个数?i-v,…,?i-1,?i,?i+1,…,?i+v(其中f2为窗口中心值,v=(m-1)/2),再将这m个点按其数值大小排序,取其序号为中心点的那个数作为滤波输出。用数学公式表示为:yi=Med{?i-v,…,?i,…,?i+v} i∈N,v=(m-1)/2

3. 结束语

实验证明:以上抗干扰方法在基于DSP的数字图像处理系统中能够充分地抑制来自系统外和系统自身的干扰,能够有效地提高系统的抗干扰能力和可靠性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)