基于Spartan-3A DSP的安全视频系统分析

单个视频和图像DSP处理器已经不能以可接受的数据速率完成某些计算密集的分析运算了,比如交通监控应用中视频分析输出。此外,也没有强大可靠的解决方案能够在全视频帧速率下处理高清晰(HD)视频数据。这也迫使系统工程师采用多芯片或其它单芯片系统。基于赛灵思的Spartan-3A DSP 3400A的方案正是满足此要求的产品。范围广泛的安全分析应用对处理带宽的要求迫使企业重新考虑系统硬件的设计方法。单个视频和图像DSP处理器已经不能以可接受的数据速率完成某些计算密集的分析运算了。此外,也没有强大可靠的解决方案能够在全视频帧速率下处理高清晰(HD)视频数据。这也迫使系统工程师采用多芯片或其它单芯片系统,不过,这两种解决方案各有其优点和缺点。

由多片DSP组成的多芯片系统一般可为设计人员提供更为熟悉的设计流程,但增加了PCB成本、占用板级/系统级空间,同时还可能带来系统性能问题。另一方面,单芯片解决方案看起来在成本、封装和功耗方面具有优势,但可能增加设计人员的学习难度,提高设计项目的复杂性和工程成本,且有可能拖延产品发布的时间。这也是视频分析公司Eutecus在开发下一代安全分析产品--多核视频分析引擎(MVE)时遇到的难题。

Eutecus的第一代安全分析产品基于德州仪器(TI)的达芬奇(DaVinci)数字媒体片上系统(SoC)平台。但第二代产品中需要更强大的处理能力和系统集成度,而多个DSP器件的解决方案无论在成本上还是在系统级效益上都没有优势。这个方案需要能方便地将上一代产品移植过来,并且能为第二代MVE提供更多特性的单芯片解决方案。

赛灵思的Spartan-3A DSP 3400A正是满足此要求的产品。该器件提供了126个专用XtremeDSP DSP48A逻辑片,可以提供足够的性能来满足我们的系统要求,并且价格也很有吸引力。

当进一步了解到赛灵思嵌入式开发套件(EDK)支持Spartan-3ADSP之后,我们对设计移植方面的担心也很快消失了。赛灵思公司的EDK嵌入式开发套件可以实现基于赛灵思MicroBlaze嵌入式处理器的双处理器硬件架构,与TI公司DaVinci平台双处理器硬件架构类似。

选定器件之后,开始将现有的基于DaVinci的代码移植到赛灵思双处理器嵌入式系统,以创造一个单芯片视频安全分析设计。然后,在FPGA构造中创建了适量的加速器模块来满足性能要求,其中包括在全帧速率下处理高清晰视频。这就是第二代MVE系统,现在已经成功地销售到航空航天/国防、机器视觉和监控市场。

视频分析产品简介

多核视频分析引擎(MVE)基于InstantVision Embedded软件和能够提供许多高级功能的专用C-MVA协处理器。

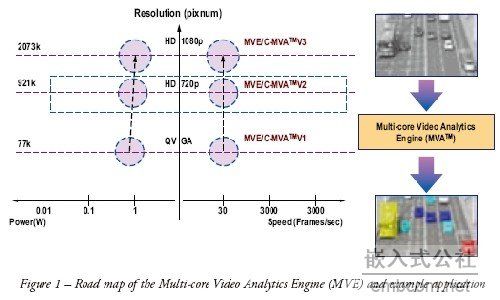

MVE/C-MVA最新版本能够以全帧速率处理高清晰视频。其功耗还不到1瓦,能够以全并行方式执行多种事件检测和分类算法。图1给出的是一个交通监控应用中视频分析输出的例子,针对不同类型的车辆、车流方向、车道变化以及违规变道等情况进行了分类,所有这些都是并发进行的并且利用不同的颜色进行了标记。

图1:多内核视频分析引擎(MVE)及示例应用的发展路线图。

设计C-MVA协处理器的目标是能够扩展其运算的复杂度以支持密集物体空间的分析功能,此时需要重叠分析和处理不完整的对象/事件,因此特别具有挑战性。专用DSP在这方面的支持性很差,而且计算可扩展能力也不好。而FPGA在这两个方面则具有更大的灵活性。

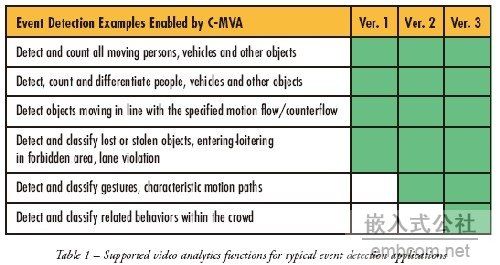

Spartan-3ADSP 3400A FPGA中的126个XtremeDSP DSP48A逻辑片能够提供高达30GMAC的DSP性能,因此完全能够满足视频分析应用苛刻的成本和性能要求。赛灵思FPGA还允许我们根据客户需求增加更多视频分析功能以及相关的事件检测事例。我们在表1中做了小结。

表1: 典型事件检测应用中支持的视频分析功能。

此外,通过赛灵思FPGA和ISE设计套件工具,视频分析设计小组可以为终端客户定制解决方案方面提供更大灵活性。通过快速建立标准分辨率和高清晰视频处理原型,我们可以快速定制视频分析引擎和片上系统(SoC)解决方案。这样我们就可以根据客户需求更高效地利用Spartan-3A DSP3400A或成本更低的Spartan-3A DSP 1800A FPGA器件中的可用资源。

FPGA解决方案另一个好处是可以利用同一硬件平台创建多种不同的衍生产品。由于我们已经使用VHDL设计了多种分析加速器引擎,因此可以将这些专用内核集成到C-MVA协处理器中。这种方法允许工程师重新利用双MicroBlaze嵌入式系统来创建不同的FPGA编程文件,这样就构成了高度可扩展的解决方案,可以轻松调节适应范围广泛的视频分析应用。

从DaVinci移植到赛灵思FPGA

我们先前一代的视频分析产品基于TI DaVinci数字媒体SoC芯片TMS320DM6?46。该芯片包括ARM9x处理器和C6?x+DSP协处理器。在设计中,我们使用ARM9x做通信和控制,用C6?x+做分析算法的DSP处理。然而,两者组合起来构成的系统仍然无法满足我们第二代产品所需要的高性能处理要求。因此,我们转向了Spartan-3A DSP FPGA系列。

通过创建拥有两个独立运行MicroBlazev7软内核处理器的赛灵思嵌入式系统,我们简化了设计移植任务。这种架构使我们可以分别移植ARM和DSP处理器代码,从而大大简化了设计移植过程。图2给出了Eutecus硬件系统的框图,以及基于MVE的参考SoC设计。

我们的MVE引擎包括运行在MicroBlaze(MB0)上的InstantVision嵌入式软件,运行在MicroBlaze(MB1)上的系统控制和通信部分以及C-MVA协处理器。C-MVA协处理器是运行在FPGA构造上的硬件加速器IP内核模块链。

利用ISE设计套件和MicroBlaze软核,我们的ARM和DSP代码移植工作相当简单。一个突出优点就是,InstantVision跨平台环境是采用高级标准C/C++语言编写的,只需要很少的修改。

Spartan-3A 安全视频 DSP 相关文章:

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)