基于DSP的继电保护测试仪信号采集系统硬件设计

,R/C,分别接DSP的中断信号引脚XINT1和通用I/O接口GPIOB0,GPIOB1。为了保证双DSP的同步采样,防止数据输出时两DSP数据的串扰,采用将另一个DSP的片选信号CS和启动信号R/C分别接DSP的通用I/O接口GPIOB2和GPIOB3的方法。这样可以保证双DSP同步采样,并依次读取两个A/D中的数据。

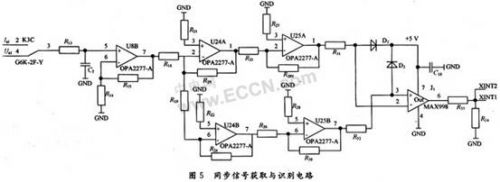

2.4 同步信号获取与识别电路设计

为了实现A/D转换器的交流同步采样,本方案的设计电路如图5所示。方案选用多个OPA2277和比较器MAX998来组成信号的获取与识别电路,从而克服了非整周期采样带来的频率泄露误差,实现严格的同步采样和等间隔采样。图5中,K3C为继电器,用作开关使用,用来通断选择获取的一路交流电压信号和一路交流电流信号。OPA2277组成放大和滤波电路。二极管D2,D3的作用是保护比较器MAX998,防止电压过大而击穿MAX998。

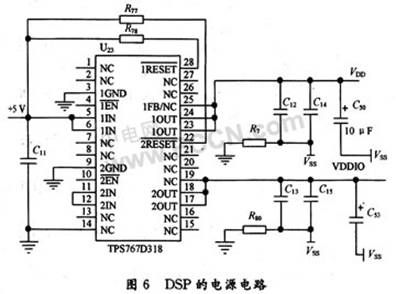

2.5 DSP系统的设计

DSP系统主要由DSP芯片、电源电路、时钟电路、仿真和测试电路组成。由于TMS320F2812的电源系统既有3.3 V的数字和模拟电源,又有1.8 V的数字电源,电源的安全和可靠是系统运行的根本保证,所以需要将常用的5 V电源转换成3.3 V和1.8 V电源。本设计选用TI公司的TPS767D318作为电源芯片,该芯片是专门为DSP的应用而设计的,可以提供3.3 V和1.8 V两路电压输出,其中每路输出均可提供最大为1 A的电流。TPS767D318同时具有电压监测功能。电源电路的设计如图6所示。此外,DSP的每个电源和地引脚不能悬空,数字模拟地要分离设计。

由于本系统对时序的要求比较敏感,所以本系统的时钟电路选用3.3 V工作电压的外部有源晶振。该有源晶振相对无源晶振信号质量更好,而且比较稳定,连接方式相对简单。通常的用法是:一脚悬空,二脚接地,三脚接输出,四脚接电压。

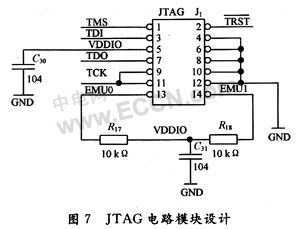

在对DSP系统进行硬件仿真时,可以通过JTAG边界扫描接口对DSP内部的数据存储器、程序存储器和控制寄存器进行在线监控,并能在TMS320F2812的开发环境CCS中把程序下载到DSP芯片进行硬件仿真。JTAG接口的原理图如图7所示。

2.6通讯模块设计

目前,数据采集系统多以ISA,EISA或PCI插卡的形式完成数据的传输,这些方式存在着开发调试比较困难、安装麻烦以及通用性和可移植性差等缺点,而且PC机上的插槽数量、地址、终端资源有限,导致这种方式的可扩展性差。目前,广泛应用的USB总线接口具有安装方便、高带宽、易于扩展等优点,已成为计算机接口的主流。本文选用专用的USB接口芯片来完成DSP与PC机的数据传输。USB 2.0芯片选用Philips公司的ISP1581。ISP1581与TMS320F2812的连接电路图如图8所示。ISP1581在上电时,通过BUS_CONF,MODE0,MODE1对接口进行设置,本设计中BUS CONF通过电阻连接至高电平,ISP1581工作在通用处理器模式,AD[0~7]是8位地址总线,DATA[0~15]是独立的数据总线。MODE0设为1,因此读写选通信号为8051类型。TMS320F2812的XCS0AND1作为ISP1581的片选信号。RREF引脚通过12 kΩ的精密电阻接地,提供精确的镜像电流。RPU引脚通过1.5 kΩ电阻器上拉。

3结语

研制了一种基于DSP技术的继电保护测试仪信号采集装置,以便检定继电保护测试仪的性能指标是否满足设计要求。文中重点介绍了数据采集装置的整体架构、基于DSP的数据采集装置的硬件组成和电路设计。该数据采集装置可以精确采集继电保护测试仪的各项数据,为继电保护测试仪的检定装置奠定了技术基础。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)