如何避免在DSP系统中出现噪声和EMI问题的方法

在任何高速数字电路设计中,处理噪声和电磁干扰(EMI)都是一个必然的挑战。处理音视频和通信信号的数字信号处理(DSP)系统特别容易遭受这些干扰,设计时应该及早搞清楚潜在的噪声和干扰源,并及早采取措施将这些干扰降到最小。良好的规划将减少调试阶段中的大量时间和工作的反复,从而会节省总的设计时间和成本。

如今,最快的DSP的内部时钟速率高达数千兆赫,而发射和接收信号的频率高达几百兆赫。这些高速开关信号将会产生大量的噪声和干扰,将影响系统性能并产生电平很高的EMI。而DSP系统也变得更加复杂,比如具有音视频接口、LCD和无线通信功能,以太网和USB控制器、电源、振荡器、驱动控制以及其他各种电路,所有这些都将产生噪声,也都会受到相邻元器件的影响。音视频系统中特别容易产生这些问题,因为噪声会引起敏感的模拟性能的下降,而对于离散的数据来说却不明显。

至关重要的是从设计的一开始就着手解决噪声和干扰问题。许多设计第一次都没有通过联邦通信委员会(FCC)的电磁兼容测试。如果在早期的设计中在低噪声和低干扰设计方法上花费一些时间,就会减少后续阶段的重新设计成本和产品的上市时间的延迟。因此,从设计的一开始,开发工程师就应该着眼于:

1. 选用在动态负载条件下具有低开关噪声的电源;

2. 将高速信号线间的串扰降到最小;

3. 高频和低频退耦;

4. 具有最小传输线效应的优良的信号完整性;

如果实现了这些目标,开发工程师就能有效避免噪声和EMI方面的缺陷。

噪声的影响及控制

对于高速DSP而言,降低噪声是最重要的设计准则之一。来自任何噪声源的过大的噪声,都会导致随机逻辑和锁相环(PLL)失效,从而降低可靠性。还会导致影响FCC认证测试的辐射干扰。此外,调试一个噪声很大的系统是极端困难的;因此,要消除噪声-如果能够彻底消除的话-则要求在电路板设计中花费大量的功夫。

在音视频系统中,即便是比较小的干扰,也会对最终产品的性能产生显著的影响。例如,音频捕获和回放系统中,性能将取决于所用的音频编解码的质量,电源的噪声,PCB布线质量,以及相邻电路间的串扰大小等。而且,采样时钟的稳定度也要求非常高,以避免出现不希望的杂音,如在回放和捕获过程中的"砰砰"声和"咔嚓"声。

在视频系统中,主要的挑战是消除色彩失真,60Hz"嗡嗡"声以及音频敲击声。这些对高质量视频的系统都是有害的,例如安全监控方面的应用。实际上,上述这些问题通常都与视频电路板的设计不良有关。具体包括:电源噪声传到视频的DAC输出上;音频回放引起电源的瞬变;音频信号耦合到了高阻抗的视频电路的信号线上。

这些典型的视频问题源包括:同步和像素时钟的过冲和欠冲;影响色彩的编解码和像素时钟的抖动;缺少端接电阻的图像失真;音视频隔离较差引起的闪烁。

音视频应用容易产生的噪声干扰问题,对于所有要求具有很低误码率的通信系统来说也是常见的。在通信系统中,辐射不仅仅产生EMI问题,还会阻塞其他的通信信道,从而引起虚假的信道检测。采用适当的电路板设计技术、屏蔽技术以及RF和混合的模拟/数字信号的隔离等技术,就可以解决这些挑战。

在高速DSP系统中有许多潜在的开关噪声源,包括:信号线间的串扰;传输线效应引起的反射;退耦电容不合适所引起的电压降低;高电感的电源线,振荡器和锁相环电路;开关电源;线形调整器不稳定性所引起的大容性负载;磁盘驱动器。

这些问题由电耦合和磁耦合共同产生。电耦合的产生是由于相邻信号和电路的寄生电容和互感所引起,而磁耦合的形成是由于相邻的信号线形成辐射天线所导致。如果辐射干扰足够强的话,将会导致能够摧毁其他系统的EMI问题。

当高速DSP系统中的噪声无法根本消除时,则应该将其减到最小。电子元器件内部都有噪声,故仔细地选择器件特性,并选用适当的器件是至关重要的。除了器件的正确选择外,还有两种通用的技术,即PCB布线和回路退耦可以帮助控制系统噪声。一个优秀的PCB布线将降低噪声通道产生的可能性。另外,还减小了能够传播到印制线和电流回路上的辐射,退耦避免相邻电路产生的噪声影响。最好的方法是从源头上滤除噪声,不过也可以使相邻的电路对噪声不敏感或者消除噪声的耦合通道。

现在我们讨论几种可以解决由系统噪声和EMI引起的许多常见问题的技术。

保持电流回路最短

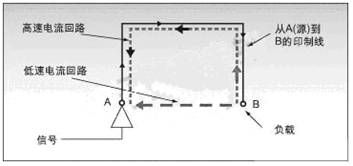

低速信号电流沿阻抗最小,即最短的路径返回源端。而高速信号则是沿电感最小的路径返回:这样的最小的回路面积位于信号线的下面,如图1所示。

图1:高速信号与低速信号电流的比较。

因此,高速信号设计的目标之一就是为信号电

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)