基于FPGA/DSP的灵巧干扰平台设计与实现

引 言

目前,通信干扰的手段以信号大功率压制为主,本质上属于物理层能量干扰,存在效费比低,且容易暴露自身目标等缺点,而且随着新的功率控制和信号处理技术的应用,通信大功率压制干扰手段的应用遇到了瓶颈。大功率压制干扰手段的局限性对研究一种新的小功率灵巧干扰技术提出了迫切的需求。美国通信干扰专家Richard A.Poisel于2002年首先提出了灵巧干扰(smart jamming)的概念。他指出可以利用接收机在捕获输入信号时间和帧同步信息的过程实施攻击,这可以看作是灵巧干扰技术的雏形。当前灵巧干扰正成为国内外研究的热点。本文设计的灵巧干扰硬件平台正是基于这种背景,可以为灵巧干扰技术的发展提供硬件平台支持。

1 灵巧干扰平台工作原理

经过前端射频选频滤波和下变频后,灵巧干扰平台将获得所测频段范围的中频信号送入高速信号处理平.台。高速信号处理平台由数/模转换器(ADC)产生数字中频信号,经数字下变频器(DDC)后送入数字信号处理器,由数字信号处理器完成信号的搜索截获、参数估计及识别,软件化的解调器根据这些处理结果选择适当的解讽方式和参数完成解调,解调器的输入来源于经过数字下变频(DDC)的数字基带复信号,通过对解调信号的分析,可以进一步识别信号的编码方式等底层信息。最终生成与侦察信号同等样式或相关度极大的干扰信号,将能量压制提升为信息压制,只要在敌我双方信息功率上形成一定的信息能量优势就可以取得很好的干扰效果。

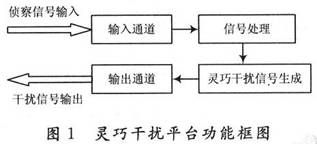

平台功能框图如图1所示。

其中,输入通道功能包括:A/D变换、数字下变频;信号处理功能主要有:信号载频估计、参数估计、调制识别、解调、编码识别等;灵巧干扰信号生成单元根据信号处理单元得到的信号参数生成干扰信号;输出通道与输入通道对应,将产生的干扰信号变换到相应的中频发出。

2 平台总体设计

2.1 平台硬件结构设计

通信侦察信号分析属于非合作通信环境下的信号处理,其宽频带、多调制方式、多信号的特点要求信号处理平台中的处理器具有高性能的处理能力外,还应具备较强的通用性、灵活性。随着大规模可编程器件的发展,采用DSP芯片和可编程逻辑器件相结合的信号处理平台显示出其优越性。采用这种结构的信号处理平台的最大特点是结构灵活,有较强的通用性,适合于模块化设计,从而能够提高算法效率;同时开发周期较短,平台易于维护和扩展,特别适合于实时信号处理。近些年,更多的实时信息处理平台采用了FPGA+DSP的结构,FPGA和DSP协作发挥各自的长处,低层的预处理算法处理的数据量大,对处理速度要求高,但运算结构相对比较简单,适合于用FP~GA进行硬件实现,这样能兼顾速度及灵活性;高层处理算法的特点是处理的数据量较低层算法少,但算法的结构复杂,适合于用运算速度高,寻址方式灵活,通信机制强的DSP 芯片来实现。

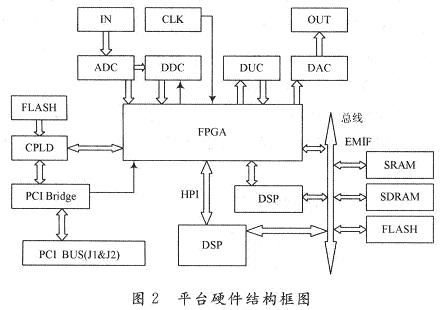

根据灵巧干扰平台功能要求,平台硬件结构如图2所示。

该平台采用CPCI结构,主要由A/D,D/A转换及DDC,DUC模块、DSP信号处理模块、CPCI总线接口、FPGA高速数字传输、存储器、PCI桥模块、CPLD模块等几部分组成。主要特性如下:

(1)单通道14 b分辨率,150 MSPS采样率的高速带宽ADC AD9254。

(2)宽带数字正交下变频DDC芯片AD6636,支持抽取与滤波。

(3)单通道14 b分辨率,300 MSPS采样率的高速宽带DAC AD9755。

(4)宽带数字正交上下变频DUC芯片GC5016,支持抽取与滤波。

(5)处理器之间(包括两片TMS320C6713 DSP芯片与一片Xilinx Virtex 4 FPGA芯片)实现了多种灵活的高速实时数据传输与交换通道。

(6)CPCI总线兼容PCI 2.2 64位/66 MHz,支持Master(DMA)/Target burst模式。

FPGA和DSP协同完成信号处理功能,这里重点说明其协同原理(见图3)。

FPGA与DSP主要通过共享EMIF总线上的存储空间进行数据交换。存储器包括:共128 MB的SDRAM,512 KB的SBSRAM,8 MB的非易失FLASH,它将大大提高数字信号的传输与处理速度。DSP外部总线EMIF各种存储器及设备资源分配如下:CE0(SDRAM),CE1 (FLASH),CE2(SRAM),CE3(FPGA)。资源分配由FPGA和DSP依靠申请总线决定,因此可以通过重新编程加以修改。对于C671 3来说,EMIF总线为32位,时钟最高为100 MHz,因此总线的数据吞吐率最高为400 MB/s。为了提高总线效率,设计中FPGA与DSP都可以独立访问:EMIF总线上的存储空间,但不能同时访问。FPGA作为EMIF总线设备之一,与 SDRAM,SB-SRAM共享数据与地址总线。同时,FPGA也是EMIF总线主设备之一,与DSP共同管理EMIF总线。也就是说,FPGA也可以主动发起访问SDRAM,SBSRAM。因此,FPGA与DSP共享EMIF总

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)