PCI与DSP的某型导弹景象匹配制导系统设计

1 引 言

本文从实时性和大容量两方面介绍了在某型导弹景象匹配制导系统中通用计算机上加入DSP加速卡实现的图像采集系统。利用DSP芯片的高速处理特性完成大部分的图像处理工作,上位机只完成辅助操作和存储系统。这种方法发挥了DSP的高速性能又具有相当大的灵活性,而且开发工具比较完善。导弹景象匹配制导系统在传输实时景物图像时要求足够的传输速度,PCI总线速度最高可达528MB/S(66MHz、64位)。这是其他总线无法比拟的速度,如ISA总线速度只有5MB/S。另外,该系统中DSP的可扩展存储空间高达1GB。这完全可以满足导弹景象匹配制导系统中图像处理的需要。

2 基于PCI总线的DSP图像采集系统

本系统主要用于敏感导弹飞行航线下面或目标地区的实时景物图像,系统拍下敏感到的图像数据并传送到DSP进行处理,然后经PCI总线把处理后的数据上传到上位机,与预存在相关器中的基准景物图像比较,以获取误差信号,形成导引指令,控制导弹飞向目标。当然这套系统也可用于其他的视频会议、视频点播以及监控系统,如大型超市监控、写字楼监控等,其硬件系统基本一致,只是软件功能有所区别。

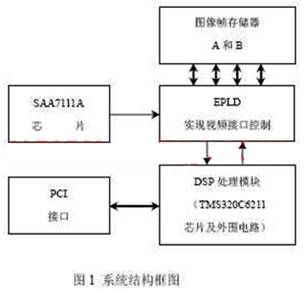

系统采用了TI公司C6000系列DSP中的TMS320C6211[1] [2]作为系统的CPU。图像数据通过光学成像或微波成像装置采集并输出模拟图像信号。这些信号经视频解码芯片转换为数字信号;再经FIFO输入DSP进行图像的增强、分割、特征提取和数据压缩等;然后输出信号经PCI解码芯片转换为符合PCI总线规范的标准信号,通过PCI总线接口传到上位机。系统的控制逻辑由EPLD(Erasable Programmable Logic Device)控制器实现。系统结构图如图1所示:

(1)视频解码芯片

系统中采集的图像信号采用Philips公司的SAA7111A[3]完成A/D转换。SAA7111A允许四路模拟视频输入,具有两个模拟处理通道,支持四路CVBS模拟信号或二路Y/C模拟信号或二路CVBS信号和一路Y/C信号。SAA7111A对摄像头输入的标准PAL格式的模拟图像信号进行A/D转换,然后输出符合CCIR601格式的4:2:2的16位YUV数据到FIFO。其中亮度信号Y为8位、色度信号Cr和Cb合为8位数据。FIFO采用IDT公司的IDT72V215LB芯片,FIFO的深度为512×18bit,支持STANDARD(标准)和FWFT(First Word Fall-Through,首字直接通过)两种工作模式。按照CCIR601[4]格式,YUV图像分辨率为720×576象素,当按行输出时,SAA7111A输出数据流大小为:720×16=1440bit。因为DSP通过32位的SBSRAM接口与FIFO通信,故YUV数据写入FIFO时需要在FIFO之间实现乒乓切换。这时一行720×16bit的数据在两片FIFO中存储变为360×32bit。两片FIFO可以满足上述要求。FIFO的初始化及时序由

EPLD实现。

(2)DSP图像处理模块

TMS320C6211是TI公司发布的面向视频处理领域的新款高速数字处理芯片,适用于移动通信基站、图像监控、雷达系统等对速度要求高和高度智能化的应用领域。存储空间分两部分:

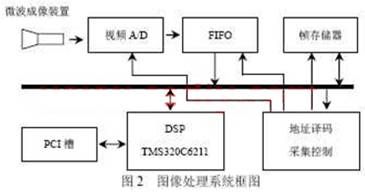

运行过程的临时数据存在Winbond公司的两片128Mbit的W981216BH[5]中;系统程序则固化在FLASH存储器中,该存储器选用AMD公司生产的8Mbit的AM29LV800B。Flash存储器具有在线重写入功能。这对系统启动程序的修改和升级都带来了很大的方便。基于TMS320C6211的图像处理系统框图如图2所示:

TMS320C6211 DSP的高速性能主要体现在以下方面:

①TMS320C6211的存储空间最大可扩展到1GB,完全可以满足各种图像处理系统所需的内存空间,而且其最高时钟可达200MHz,峰值性能可达1600MIPS(百万条指令/秒)、2400MOPS(百万次操作/秒)。

②并行处理结构。TMS320C6211芯片内有8个并行处理单元,分为相同的两组,并行结构大大提高芯片的性能。

③芯片体系采用VelociTI结构。VelociTI是一种高性能的甚长指令字(VLIW)结构,单指令字字长为32bit,8个指令组成一个指令包,总字长为256bit。即每秒钟可以执行8条指令。VelociTI结构大大提高了DSP芯片的性能。

④采用流水线操作实现高速度、高效率。TMS320C6211只有在流水线充分发挥作用的情况下,才能达到最高的峰值性能。与其他系列DSP相比,优势在于简化了流水线的控制以消除流水线互锁,并增加流水线的深度来消除传统流水线的取指、数据访问和乘法操作上的瓶颈。

本系统DSP主要完成从FIFO读出数据的处理以及压缩等。数据处理由自行编写的算法实现,数据压缩算法采用JPEG(Joint Photographic Expert Group)标准。当光学成像或微波成像装置采集速度为每秒25帧图像时,它留给DSP处理的时间最多为每帧40ms。如果考虑系统有一定的延时以及处理后图像的存储时间,那么DSP处理一幅图像时

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于DSP的PCI驱动程序开发 (04-08)