基于DSP CPLD信号采集系统通讯接口设计

0.引言

随着数字信号处理技术理论的不断发展,数字信号处理器的发展也是日新月异。不仅执 行指令速度越来越快,而且其功耗也越来越低。许多仪器或检测设备都不约而同地将DSP 应用到那些数据量庞大而且需实时传送数据的系统中。核信号数据采集系统也不例外,利用 DSP 可以实时有效地处理采集的信号,并将处理数据发送至上位机进行进一步处理。通常 数据采集系统下位机与上位机的通讯采用串口方式,这种方式不仅协议简单,而且连接方便。

但是这种方式的数据传送速率不高,而USB 总线接口具有方便快捷、支持即插即用、可实现高速数据通讯等优点,在很多领域得到广泛应用。USB 总线接口在USB1.1 协议下传输速率可达12Mbps ,USB2.0 协议下可达480Mbps ,完全可以满足目前的数据采集控制系统对于 数据实时传输速率越来越高的要求。因此在本系统设计中其通讯方式采用USB(Universal Serial Bus)总线接口方式。 USB 控制芯片采用Cypress 公司EZ-USB SX2 系列的CY7C68001 控制芯片,DSP 选用TI 公司的定点DSP 芯片TMS320VC5502。

1.CY7C68001USB 控制芯片介绍

CY7C68001 是由美国Cypress 公司开发的高速USB 芯片,支持USB2.0 协议。其内部 集成有USB 收发器(物理层)、USB 串行接口引擎SIE(链路层,实现底层通信协议)、4KB的FIFO 以及电压调节器、锁相环;可工作于全速(12Mb/s)和高速(480Mb/s)两种传输模式, 支持8 位和16 位数据总线方式,具有同步和异步的FIFO 接口。CY7C68001 被用来与DSP、 ASIC、FPGA 等控制器连接实现USB 的功能,其内部不含微控制器。同时CY7C68001 提供4 种传输方式(控制传输、中断传输、批量传输和同步传输),可满足用户对各种传输方式的要求。由于该控制芯片内不含微控制器,USB 的应用层协议应该由DSP 编程实现,USB 固件的加载必须靠DSP 控制CY7C68001 完成。

2.通讯接口系统硬件设计

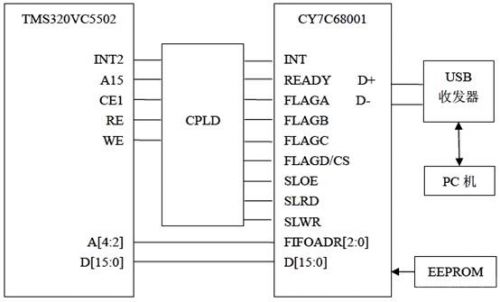

整个采集系统包括的部分有传感器信号调理电路、A/D 转换电路、FIFO 数据缓冲单元、 DSP 控制器、FLASH 程序存储单元、CPLD 逻辑控制单元、与上位机连接的USB 通讯单元。 其中与PC 机通讯的USB 单元硬件接口框图如下图所示。

图 1 数据采集系统与PC 机通讯的硬件接口框图

由图 1 可以看出,通讯部分主要由CY7C68001 USB 控制器、CPLD 逻辑单元、E2PROM、 TMS320VC5502 组成。由于整个系统所需的器件数目较多,由此带来的逻辑控制较为复杂, 而DSP 的I/O 接口有限,故在系统中加入了CPLD 逻辑控制单元,用于产生电路中需要的 逻辑状态。同时用CPLD 中还实现了寄存器功能,这部分寄存器用于表征USB 通讯时各种状态信息,便于DSP 查询。

CY7C68001 USB 控制器与TMS320VC5502 采用EMIF 连接方式,并将USB 控制器中 的存储器配置到CE1 空间。同时采用异步读写方式完成TMS320VC5502 与CY7C68001 之 间的数据和命令交换。系统中E2PROM 的作用是完成USB 控制器的描述表自举。CY7C68001 控制器的自举方式有两种:EEPROM 和微控制器,本系统采用EEPROM 方式。

3.通讯接口系统软件设计

3.1 主机端软件设计

主机端软件的功能主要是完成下位机上传数据的接收、显示、分析等。由于信号采集的 数据量较大,所以在USB 传输方式上采用批量传输方式。 主机端软件的设计包含3 个方面:

(1)USB 驱动程序设计

USB 驱动程序的功能主要是实现USB 发现、配置、关闭以及数据的传送接口控制。 USB 设备驱动程序的设计是基于WDM (Windows driver model ,驱动程序模型)的。WDM 采用分层驱动程序模型,分为较高级的USB 设备驱动程序和较低级的USB 函数层。其中 USB 函数层由两部分组成:较高级的通用串行总线模块(US-BD)和较低级的主控制器驱动程 序模块(HCD)。在上述USB 分层模块中,USB 函数层由操作系统提供,负责管理USB 设备驱动程序和USB 控制器之间的通信、加载及卸载USB 驱动程序,与USB 设备通用端点建立通信来执行设备配置、数据与USB 协议框架和打包格式的双向转换任务。

(2)安装USB 的信息文件(.inf)

这一步用于将驱动程序绑定到特定设备的Verdor ID (VID) 和Product ID( PID)。当USB 设备插入计算机时,计算机检测到设备插入后自动发出查询请求;USB 设备回应该请求, 并送出设备的VID /PID。计算机根据这两个ID 装载相应设备驱动程序,完成枚举。

(3)用户应用程序

用户应用程序是数据采集系统的核心,其主要功能为:开启或关闭USB 设备、检测USB 设备、设置USB 数据传输管道、设置A /D 状态和数据采集端口、实时从USB 接口采集数据、显示并分析数据。整个应用程序采用

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)