DSP高速系统的电路板级电磁兼容性设计

号线的布置

不相容的信号线之间能产生耦合干扰,所以在信号线的布置上要把它们隔离,隔离时采取的措施有:

(1)不相容信号线应相互远离,不要平行,分布在不同层上的信号线走向应相互垂直,这样可以减少线间的电场和磁场耦合干扰;

(2)高速信号线特别是时钟线要尽可能的短,必要时可在高速信号线两边加隔离地线;

(3)信号线的布置最好根据信号流向顺序安排,一个电路的输入信号线不要再折回输入信号线区域,因为输入线与输出线通常是不相容的。

当高速数字信号的传输延时时间Td>Tr(Tr为信号的脉冲上升时间)时,应考虑阻抗匹配问题。因为错误的终端阻抗匹配将会引起信号反馈和阻尼振荡。通常线路终端阻抗匹配的方法有串联源端接法、并联端接法、RC端接法、Thevenin端接法4种。

(1)串联源端接法

图3为串联源端接电路。

源端阻抗Zs和分布在传输线上的阻抗Zo之间,加上源端接电阻Rs,用来完成阻抗匹配,Rs还能吸收负载的反馈。这里的Rs必须离源端尽可能的近,理论上应为Rs=Zo-Zs中的实数值。一般Rs取15~75Ω。

(2)并联端接法

图4为并联端接电路。附加1个并联端电阻Rp,这样Rp与ZL并联后就与Zo相匹配。这个方法需要源驱动电路来驱动一个较高的电流,能耗很高,所以在功耗小的系统中不适用。

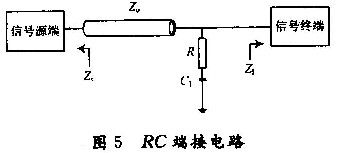

(3)RC端接法

图5为RC端接电路。该方法类似于并联端接电路,但引入了电容C1,此时R用于提供匹配Zo的阻抗。C1为R提供驱动电流并过滤掉从传输线到地的射频能量。因此与并联端接方法相比,RC端接电路需要的源驱动电流更少。R和C1的值由Zo,Tpd(环路传输延迟)和终端负载电容值Cd决定。时间为常数,RC=3Tpd,其中R∥ZL=Zo,C=C1∥Cd。

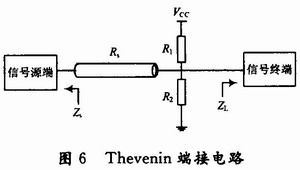

(4)Thevenin端接法

图6为Thevenin端接电路。该电路由上拉电阻R1和下拉电阻R2组成,这样就使逻辑高和逻辑低与目标负载相符。其中,R1和R2的值由R1∥R2=Zo决定,R1+R2+ZL的值要保证最大电流不能超过驱动电路容量。

3 结语

本文通过对电子产品电磁环境的分析,确定高速DSP系统中产生干扰的主要原因,并针对这些原因,通过对高速DSP系统的多层板布局、器件布局以及PCB布线等方面进行分析,给出有效降低DSP系统的干扰、提高电磁兼容性能的措施。从设计层次保证了高速DSP系统的有效性和可靠性。合理布局设计,减少噪声,降低干扰,避开不必要的失误,对系统性能的发挥起到不可低估的作用。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)