基于DSP和80C196双CPU构成的高速实时控制系统

时间:01-11

来源:3721RD

点击:

可以满足TMS320C31的要求,这样IDT7140的/INTL引脚就可以和TMS320C31的INT1直接相连。但与此同时也要求TMS320C31尽快地服务IDT7140的中断申请,以免一个中断申请被误认为多个中断申请。

4 TMS320C31与80C196之间采用双口RAM进行高速数据通信的软件实现

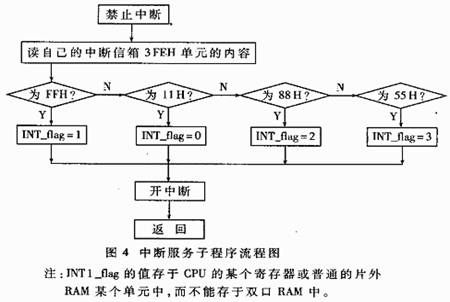

从图2中我们得知,左边CPU写右边CPU的中断信箱3FFH单元时,双口RAM会给右边CPU发一中断信号;同样,右边CPU在写左边CPU的中断信箱3FFH单元时,双口RAM也会给左边CPU发一中断信号。以左边的TMS320C31为例,在它获得外部中断信号INT1后,它并不知道右边的80C196是刚开始占用双口RAM还是用完了要释放使用权,或者是其它别的意思。所以双方事先应有一个简单的协议,例如右边CPU在3FEH单元中(或右边CPU在3FFH单元中)写"FFH"代表右(左)边正占用双口RAM,定"11H"代表要释放使用权,或者还可以有更多的数据含义的定义,视两边CPU通信内容的复杂程度而定。例如在这个高速实时控制系统中,还定义了"88H"和"55H"来表示其它的含义。这样,在中断服务程序里,就可以做相应的操作。下面以TMS320C31为例来说明数据通信的软件实现,程序流程如图3和图4所示。

随着各种复杂算法的应用越来越广泛,DSP的应用也会越来越普及,各种不同的多CPU系统不断涌现。在这些系统中,双口RAM以它方便、快速的特点将成为很多多CPU系统中的通信途径。

作者:陈云窗 侯朝桢 汤霞清

DSP 80C196双CPU 高速实时控制系统 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)