基于DSP的H.264编码器的电路设计

C6000编译器提供了许多内联函数intrinsics,它们是汇编指令映射的在线函数,不宜用C语言实现其功能的汇编指令都有对应的intrinsics函数。这样就可在C语言结构中直接使用内联函数实现对多个数据的并行运算操作。如:未使用内联函数优化前X264程序调用一次双线性内插函数只能计算一个亚像素点的值,而使用内联函数_mem4()、_avgu4()等进行优化后,一次可以计算4个亚像素点的值,大大提高了运算速度。②使用线性汇编语言优化:由于线性汇编不需要考虑寄存器分配、指令延迟、并行指令安排等因素。因此可以利用CCS提供的profile分析工具将使用频率高、耗时多的函数抽取出来,根据事先已知的数据间的相关性等信息,在程序中直接改写函数汇编,人工优化。涉及的算法有:SAD、SSD的计算;DCT变换;反DCT变换、亚像素搜索等。

4 实验结果

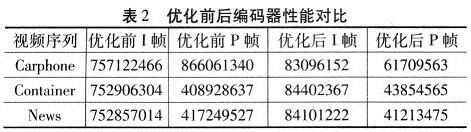

选取具有代表性的视频序列carphone(人物运动幅度较大)、news(背景变化,人物运动幅度不大)、container(背景简单,景物运动缓慢)进行编码。视频为YUV 4:2:0格式.QCIF,量化步长定为26,共50帧,采用IPPP…编码模式。DM6446的时钟频率为600 MHz。表1为优化后峰值信噪比、消耗时钟周期、码率等实验结果。表2为优化前后编码时钟周期对比,I帧编码速度平均提高了9倍,P帧编码速度平均提高了11倍。

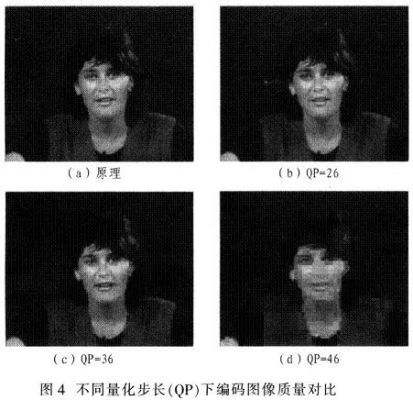

以视频Miss-America为例,研究、对比移植优化后的编码器在不同的量化步长值(QP)下,图像的压缩质量,如图4所示。

5 结论

移植优化后的X264编码器在CCS环境下可正确编码,在量化步长值26下编码图像质量较高,优化后编码速度较优化前有明显提升。介绍的H.264视频编码系统的硬件设计,和X264编码器针对DM6446平台移植、优化的思路和方法,对构建高效的视频应用平台具有一定的参考价值。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)