DSP系统电磁兼容的设计

3. 2 滤波技术

在电子系统设计时经常在电路中加入电容器来满足系统工作时所要求的电源平稳和洁净度。

根据电容在电路中的作用可分为:去耦电容、旁路电容和容纳电容。去耦电容用来滤除高速器件在电源板上引起的骚扰电流;旁路电容可用来消除高频辐射噪声,从而抑制共模干扰;容纳电容则配合去耦电容抑制由电流变化引起的噪声。

主要的滤波技术包括:

对电源线和所有进入PCB的信号进行滤波

旁路快速开关器件

旁路模拟电路的所有电源供电和基准电压引脚

在器件引线处对电源/地去耦

用多级滤波抑制不同频段的电源噪声

3. 3 其它降噪措施

根据系统功能和实现目标要求可以采用悬浮地、单点接地、多点接地和混合接地等不同的接地方式

在适当的地方加屏蔽

对有干扰的引线进行屏蔽或绞在一起以消除相互耦合

在感性负载上用箝位二极管等。

4 DSP应用系统的电磁兼容设计

DSP系统具有高精度、小功率、快速逻辑等特点,容易受到寄生阻抗、介质吸收或高频噪声的影响 。在高速数字电路中,特别是在快速DSP中,时钟电路通常是宽带噪声的主要和最大产生源,可产生高达300MHz或更高的的谐波干扰,应采取措施加以克服。此外,系统复位线、中断线和控制线是较容易受到干扰的敏感设备。

一个电子系统的电磁兼容性很大程度上取决于元件的布局和导线的连接形式。当一段导线和相应的回路中有电流流动时,便产生了天线效应,向外辐射电磁能量,此能量的大小与流过电流的幅值、频率及该电流环路所包围的面积有关。从而形成了一个典型的电磁干扰源。

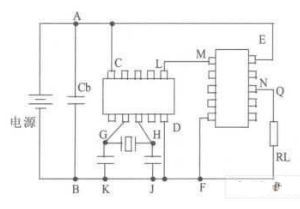

图3 电子系统内部的电流环

如图3所示,环路A-C-D-B和A-E-F-B中传输着系统正常工作所需的能量。然而电路中所消耗的能量不是恒定不变的,这主要取决于系统中各元件的瞬时工作状态。系统中每个器件动作所引起的变化都将反映到这些传输线上。为了防止电流的快速变化引起的干扰,可借助电容Cb加以抑制。由信号线和控制线形成的回路N-F-P-Q 和L-M-F-D所包围的面积相对较小,但是由它们引起的高频噪声也是不容忽视的。由晶振等元件组成的环路G-H-J-K,通常是系统中信号频率最高的区域,在进行电磁兼容(EMC)设计时应当重点考虑。

由以上分析可见,在DSP应用系统设计时要重点考虑电源线、高频信号线和时钟振荡电路的设计。

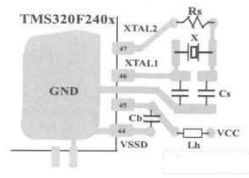

对于电源线来说,可以采用去耦电容和铁氧体保持供电电源的稳定。信号线及其回路组成环路包围的面积越小越好,以减小辐射干扰( EM I) 。在数字系统中时钟信号通常是频率最高的信号。以图4 为例,当晶振连接C24x系列内部振荡器时,通过减小高频电流和电流环路包围的面积来抑制电磁干扰。

图4 一种推荐的PCB设计方法

晶振具有很高的阻抗(通常为几百千欧) ,因此其工作时产生的高频电流幅值很小。然而CMOS电路的输出是含有高次谐波分量的方波信号,晶振自身对这些信号不具有高阻抗特性,从而将产生较大的谐波电流,可以加一个串联电阻加以抑制。两个旁路电容对振荡器产生的高频信号来讲,呈现出低阻特性,将在Cs-X-Cs之间产生较大的电流。为了减小辐射干扰,在设计时应尽量缩小这个区域的面积。

图中串联电阻阻值在一千欧范围内。

5 结束语

针对具体的DSP应用系统,应根据所选芯片类型和功能特点进行电磁兼容设计。例如TMS320C24x DSP,它除了配置有高速数字信号处理的结构,还具有单片电机控制的外设功能,是专门为数字电机控制和其他控制应用系统而设计的。当PCB设计完成后,还可以将C24x PWM单元设置为异步、同步或空间矢量PWM模式,进一步降低电磁干扰。增强系统的电磁兼容性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)