基于DSP_C54X窄带中频抽样的理论与实现

1 引言

随着DSP技术的广泛应用与迅速发展,现已深入到通信与电子系统的各个领域。软件无线电是通信领域发展中的前沿技术之一,它集数字信号处理、DSP/FPGA、无线通信和计算机软硬件技术于一体,充分体现了现代通信技术的高性能特点。本文在讨论基本的带通抽样定理基础上,分析欠抽样率对带通信号采样的频谱搬移特点,同时结合对普通的AM调幅接收机中频信号的采样、滤波与处理,以获得基带的语音信号。这种用软件进行信号处理的技术有助于深入理解带通抽样滤波的理论,并为软件无线电接收数据信号提供理论与实践依据。本文讨论的中频窄带抽样实现的基本框图如图1所示。

信号采集的前面部分可以是普通AM接收机,输入信号是fx,通过混频输出的中频信号fi=fl-fx,这里确定fi=465kHz,信号带宽是10kHz。AD转换的采样频率是fs=60kHz,直接采集窄带中频信号,经DSP处理后,通过DA输出语音信号。这一工作过程采用了带通抽样理论。

2 带通抽样理论和DSP硬件电路

2.1 带通抽样理论

带通抽样定理是Nyquist抽样定理的进一步扩展。Nyquist抽样定理的基本意义是:一个频率限带信号x(t),其频带限制在(0,fh)内,如果用fs>=2fh的采样频率对x(t)进行等间隔抽样,得到的离散信号x(n)=x(nTs),那么x(t)信号将被所得到的采样值x(n)所确定,抽样后的信号频谱不发生混叠,因此可以用滤波器恢复原始的限带信号x(t),该信号是零频附近的基带信号。而实际接收的无线电信号绝大多数是一个有中心频率的限带信号,并且满足信号带宽与中心频率之比远远小于1(B/fo<<1)的条件,即中心频率fo远高于信号所携带频谱宽度,根据基本抽样定理知道,此时抽样频率fs>2fo,这样不仅要求高性能的AD转换器,而且高速的抽样数据又大大的加剧了DSP的信号处理负担。为了让DSP有足够的时间去处理实时的信号,当前主要的方法有两种:(1)直接降低抽样率;(2)进行高速抽样,然后采用抽取方法降低抽样率。本文采用的是直接降低抽样率的方法。那么降低抽样率是否会产生信号混叠等问题呢?这由带通抽样理论来回答。

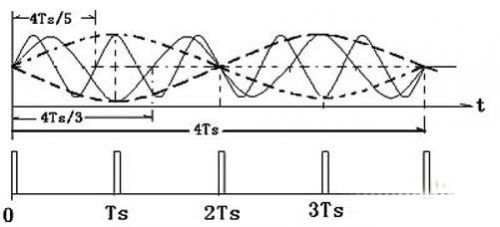

带通抽样定理:设一个频率限带信号x(t),其频带限制在(fL,fH)内,如果采样频率fs满足: 其中n取值是满足fs≥2B(B=fH-fL)的最大整数值(0,1,2,...),此时用fs进行等间隔抽样的x(nTs)能准确的确定原始信号x(t)。并确定带通信号的中心频率,那么。这个表达式表示:当抽样频率确定后,有许多频率(或带通信号)在满足以上表达式所取的n值条件下,可以产生同一个频率(或同一个带通信号);同样对于确定的fo通过选择不同的n来确定fs。如图2所示。

其中fs是抽样频率,当被抽样的信号频率fo是3fs/4和5fs/4时,都不满足fs>2fh的条件,是欠抽样情况。在欠抽样后都会输出一个相同频率的信号fs/4,如黑粗的虚线所示。进一步讲,如果被抽样的信号是一个以fo为中心频率的限带信号,带宽是B,且抽样频率fs>2B,那么欠抽样后将会输出一个以抽样频率fs/4为低中心频率的限带信号。当然抽样时不容许被抽样的信号中混入其他信号,即必须是一个限带信号,否则其他满足以上公式条件的信号都会进入该频带;其次根据自然抽样定理,输出的频谱中还会有与fs倍频有关的频谱分量,即输出信号频谱Xs是:

这需要通过DSP设计滤波器,恢复原始信号x(t)。Cn是抽样脉冲傅里叶级数的系数。根据前面介绍的参数,抽样频率是60kHz(8bit)、被抽样信号是465kHz的普通调幅接收机的中频信号是一个限带信号,信号带宽是B=10kHz。

2.2 DSP硬件电路设计

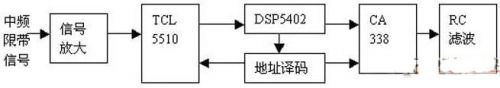

实现带通抽样,使用DSP5402作为基带信号处理,基本框图如图3所示。

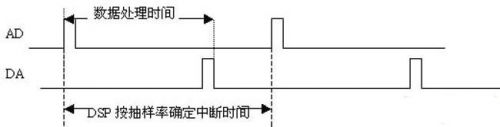

其中AD采用TCL5510,该芯片最高抽样率是20MHz,8位数据宽度,其输入信号的动态范围是0.6~2.6V,由于输入是465kHz交流的调幅信号,因此该输入信号需要叠加在被抽样信号中心位置1.6V直流电平上,AD前放大电路的输出要调整在这个电平。AD转换时钟是使用DSP_CLKOUT信号,经过2分频获得(10MHz)。

DA采用CA338,该芯片也是8位数据宽度,直接输出模拟信号。系统采用一个AD与一个DA,因此在程序设计中使用PORTR和PORTW指令,产生IO读写信号,与普通的或门控制,实现对AD的读和对DA的写操作。

3 抽样频率确定与滤波器的实现

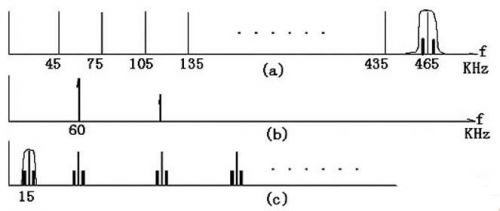

根据以上讨论,对于窄带中频信号465kHz,通过60kHz的抽样,产生15kHz的信号。抽样前后的信号频谱关系如图4所示。

其中图4(a)表示除了465kHz的带通信号可以通过欠抽样产生15kHz的低中频信号外,其他信号也可以通过欠抽样产生15kHz低中频,因此465kHz的中

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)