如何处理好嵌入式DSP设计中的功耗优化

图1:功耗估算

低功耗设计

具有功耗意识的设计(Power-conscious design)技术可以帮助DSP设计人员充分利用正确的功率估算。在系统级,设计人员应该精心选择相关元件,使其数目尽可能地低。此外,设计人员还应该考虑到哪些未使用的元件可以置于省电模式,尤其是在待机期间。板级存储器的使用也是一个功率消耗源,因为必须同时给存储器芯片和电路板迹线供电。

应用应该尽可能地使用DSP的内部存储器,以保持片上大带宽存储,把外部存储器保留用作偶尔的低速存取。片外存储器也可以很好地完成启动工作,但应该在启动后被置于省电模式。为了减少存储器中的代码量和所取指令的数量,应该优化软件提升性能。更紧凑的代码有助于更好地利用缓存和内部指令缓冲器,而且运行速度更快,故能减少系统处于激活模式的时间。

大多数特定设备都是利用DSP的内建硬件能力来降低功耗的。从一启动开始,应用设备就 可以让不使用的模块处于空闲状态,外设功耗只限用于那些在指定时间才需要的I/O 。应用通常在启动时就直接控制各个模块,稍后,DSP内核可以后台执行一个循环来检测哪些功能不需要,然后把它们关断。如果应用采用了这些技术,芯片的睡眠模式就可以把空闲期间内核及芯片的功耗降至最低。

若所要求的总体性能不等于设备的全部能力,则可以在启动时就对DSP内核电压和频率(V/F)进行调节。若系统在具有不同性能负载的应用间更替,V/F调节也可以在运行期间动态进行。要实现V/F调节,设计必需提供DSP外部电源电压控制,以及内建于后台循环程序的软件控制。由于频率调节减慢内核的运行速度,设计人员在应用设计中应该考虑到相互关联的各个操作间的时序问题。

OS中的功率管理

不论是通过V/F调节还是通过低功耗模式来动态改变系统的功率要求,都需要涉及到DSP的实时操作系统(RTOS)。RTOS中的功率管理(PM)模块能够在启动时实现功耗节省,并在整个系统上协调各个低功耗操作。

内核频率调节会影响子系统操作的时序,因此PM能够在完成频率调节之后进行时钟调节。如果对应用来说OS时钟精度不重要,或者是用户希望节省空间,则可以不使用PM功能

此外,当线程被阻断时,用户还可以激活或停用自动使时钟处于空闲状态的PM功能。在其协调作用中,PM提供了一种用于功率事件通知的注册功能,当特定功率管理事件发生时,客户可以注册通知,由于系统的复杂性,PM支持多个客户端并允许客户延迟事件的完成。

PM还提供了一个应用编程接口(API)库,可实现芯片的低功率技术软件控制。通过这些API,应用能够门控时钟,激活睡眠模式并安全管理V/F调节设置点之间的晶体管。这些设置点作为调节参数,使V/F能够按照正确的顺序降低和提高,而且具有正确操作所必需的设置时间。

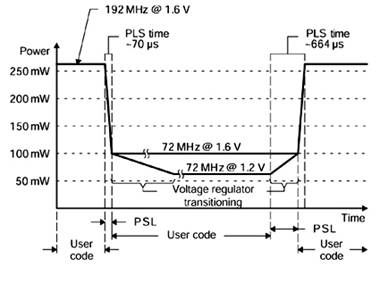

下面图2显示了设置点是如何控制V/F调节的时序的。由于电压和频率调节对设计中所用的DSP和电压调节器是特定的,PM API支持设置点延迟查询和配置,同时PM库可被重建。

图2:功耗调节结果

工具的辅助开发功能

要有效解决上述所有技术问题,需要一些专门为功率管理而设计的工具。类似于DSP工具开发的其它领域,功率优化工具也致力于提供可视化和易于使用的优势,以帮助简化系统分析并缩短上市时间。

这些工具结合DSP的嵌入式及RTOS功率管理技术,可以提供计量表、示波器波形、信道校准、测试代码和事件触发等等测试功能。利用这些便捷功能,设计人员可得到一个反馈机制,凭此评估各个实现方案对功耗的影响,最终获得一个最佳方案。

从一开始就进行功率设计

在系统开发中,功率优化有时被当作一项事后工作来处理,但这是不对的。在开发周期中,越早考虑功率优化问题越好,对于具有多个应用和工作模式的复杂系统而言尤其如是。为了延长电池工作时间,低功耗通常是主要的要求之一,即使是线路供电系统也需要通过降低耗电量来减少散热和运行成本。

为了优化功耗,设计人员需要了解系统的功率分布,以提供全面的参考信息源,从而在功率估算中把所有主要的系统功能都考虑在内。基于高功率效率的CMOS工艺的DSP集成了硬件技术,比如精细定义的低功率模式和电压/频率调节。API使这些技术很容易通过RTOS实现应用控制,测试工具可帮助设计人员估算出不同实现方案的功耗。利用这些资源,开发人员有充分的理由从开发周期的最开始就进行功率设计。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)