基于FPGA的FIR数字滤波器设计与仿真

时间:06-27

来源:

点击:

路的输出引脚。其中,引脚RD、ADCS分别与A/D转换器的引脚RD、CS相连,而引脚WR、LDAC、DACS分别与D/A转换电路的引脚WR、LDAC、CS相连。

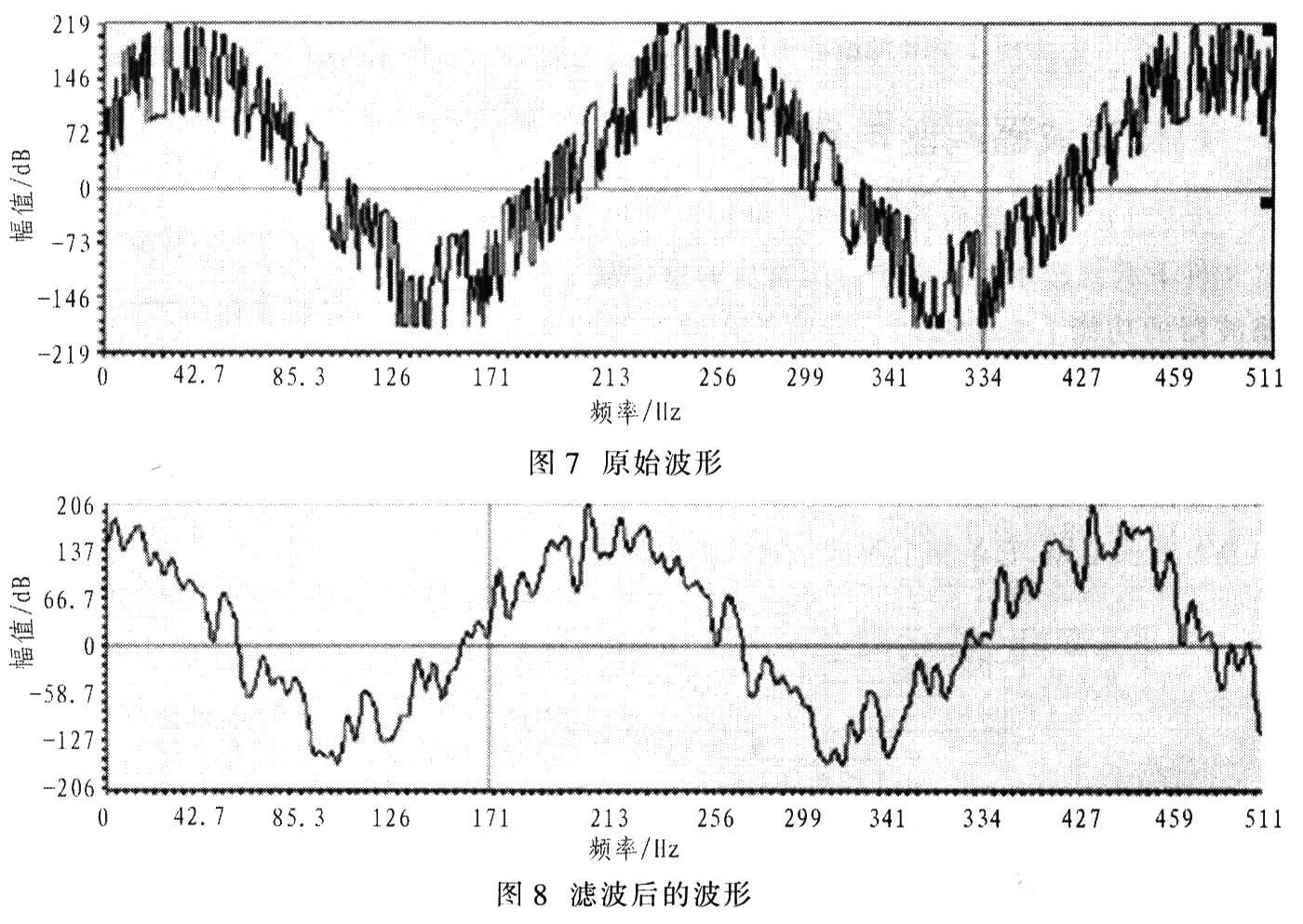

5 滤波效果测试

将设计的低通滤波器的配置文件下载到器件中进行实际滤波测试,用示波器观察各个频率点上输出信号的幅值大小。由滤波测试结果可知,该FIR滤波电路完全达到低通滤波器5 MHz的采样频率,1.5 MHz的截止频率,以及16阶的技术指标参数。图7为原始波形,图8为滤波后的波形。

6 结语

研究了在FPGA中采用分布式算法实现FIR滤波器的原理和方法,设计了FIR滤波器并借助Altera公司的FPGA器件和0uartusⅡ软件对设计方案进行仿真验证,测试结果完全能满足系统设计要求。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)