基于DSP嵌入式技术的智能刹车控制系统研究

本文在硬件电路设计上采用DSP 芯片和外围电路构成速度捕获电路,电机驱动控制器采用微控制芯片和外围电路构成了电流采样、过流保护、压力调节等电路,利用CPLD实现无刷直流电机的转子位置信号的逻辑换相。在软件设计上,软件以C语言和汇编语言相结合的方法实现了系统的控制。最后提出了模糊控制调节PID参数的控制策略。

1 引言

赛车刹车系统是赛车系统上具有相对独立功能的子系统,其作用是承受赛车的静态重量、动态冲击载荷以及吸收赛车刹车时的动能,实现赛车的制动与控制。其性能的好坏直接影响到赛车的快速反应、安全制动和生存能力,进而影响赛车的整体性能。本文设计了赛车全电防滑刹车控制器的硬件和软件,最后研究了适合于赛车刹车的控制律。

2 系统硬件电路设计

本赛车刹车控制器是由防滑控制器和电机驱动控制器组成。两个控制器都是以DSP芯片为核心。防滑控制器主要是以滑移率为控制对象,输出给定的刹车压力,以 DSP芯片为CPU,外加赛车和机轮速度信号调理电路等。电机驱动控制器主要是调节刹车压力大小,并且控制电动机电流大小,也是以DSP芯片为CPU,再加外围电路电动机电流反馈调理电路、过流保护电路、刹车压力调理电路、四组三相全桥逆变电路等构成电机驱动控制器。

2.1 DSP的最小系统

DSP的最小系统主要涉及存储器扩展、JTAG接口配置、复位电路、ADC模块的设置以及时钟电路的设计等。

1、片外存储器扩展。

片外存储器是为了弥补DSP内部RAM的不足,同时也考虑到调试过程中可以方便将程序下载到片外高速StaTIc RAM中。外部的静态随机存储器采用CY7C1041CV33。DSP既可以使用片内程序存储器,也可以使用片外程序存储器,这由引脚XMP刀MC决定的。JTAG接口。在程序需要调试时,程序下载是通过JTAG接口完成的,这个接口经过仿真器与PC机的并行口相连。

2、复位电路与时钟源模块。

用阻容电路产生上电复位和手动复位的低电平复位电路,产生复位信号。外加一个硬件看门狗,其输出端产生复位信号WDRST。电源芯片的两个输入都为+5V,输出为+1.9V和+3.3V电源为DSP供电,输出电源分别有两个复位信号,当电源不稳或过低时,将产生复位信号。

3、模数转换ADC模块的硬件配置。

模数转换ADC输出电压2V,要求输出端接一个低的ESR容量为10μF的陶瓷电容到模拟地。如果软件设置在外部参考模式下,ADCREFP能够接外部输入为2V的参考电压,并且接一个低的ESR容量为1μF到10μF的电容。否则,AD的内部参考源的精度将受到影响。

2.2赛车前轮与刹车机轮速度信号处理电路

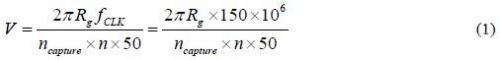

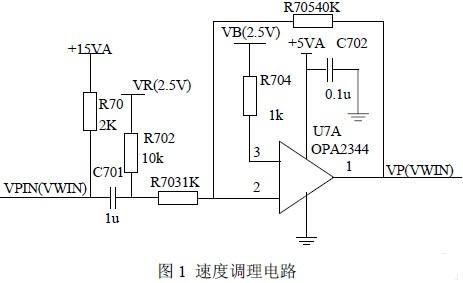

赛车防滑控制器主要是以滑移率为控制对象,防止赛车打滑,由滑移率的偏差大小调节后输出压力参考值,以跟踪给定的滑移率大小。防滑控制器上必须有赛车前轮和刹车机轮速度信号的调理电路,主要是为了得到反馈的滑移率。赛车速度信号是以自由滚动的赛车前轮速度信号代替。在赛车的前轮与刹车机轮上都装有测速传感器,当轮子转动时,测速传感器会产生正弦波形式的交流信号,机轮每转动一圈,测速传感器发出50个周期的正弦交流信号。正弦交流信号的振幅随轮子速度的变化而变化,其信号为偏压2.5V,峰值为0.3V,最大信号幅值不超过5V的正弦波信号。将此正弦波信号转换成同频率的方波后送入DSP的捕获单元,捕获方波相邻上升沿的计数值间隔ncapture,即可计算得到轮子的转速值V。由于CPUCLK为150MHz,捕获时基为其中的一个定时器,n为 CPUCLK的分频系数,凡为轮子的滚动半径,那么轮子速度的计算式为:

调理电路如图1所示:

2.3 逻辑信号电路

电机驱动器选用ALTERA公司的MAX7000A系列器件对电机的转子位置等信号进行逻辑处理,选用多达有76路可编程I/0口和100引脚的 EPM7128AE,该CPLD能够满足系统设计要求。器件EPM7128AE实现了电机的三相全桥逆变电路触发信号、过流保护、正反转、三相全桥的开通与关断等功能。一片CPLD器件EPM7128AE上有两个电机的逻辑信号。由于无刷直流电动机的霍尔位置传感器CS3020的输出是集电极开路结构,故上拉2KΩ电阻,再把霍尔信号SA, SB, SC送到CPLD的输入端口。其JTAG接口的TMS, TCK, TDI, TDO四个端子必须接上拉电阻,再接+5V电源。

2.4 无刷直流电动机的功率驱动电路

无刷直流电动机的功率驱动电路采用以IR公司的专用驱动芯片IR2130为中心的6个N沟道的MOSFET管组成的三相全桥逆变电路。其输入为以功率地为地的PWM波,送到IR2130的输入端口,输出控制N沟道的功率驱动管MOSFET,由此驱动无刷直流电动机。采用这种驱动方式主要是功率驱动芯片 IR2130对"自举"技术形成悬浮的高压侧电源的巧妙运用,简化了整个驱动电路的设计,

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)