AVS解码器在DSP平台上的优化

时间:04-13

来源:电子发烧友

点击:

成一帧图像的解码共发生4 ×M 次代码冲刷,较改进之前减少冲刷次数4 ×M ×(N - 1)。

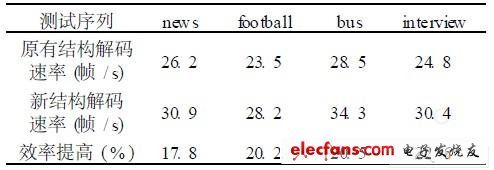

表1中的测试序列分辨率为720 ×576,调整结构后解码速率均有不同程度的提高,通过对统计结果的平均得知,效率提高20%左右。

表1 实验结果

3 结论

本文解码器优化充分利用了处理器的程序Cache功能,模块分配方式依据Cache大小而定,针对不同处理器的不同Cache, 可以有不同的模块划分方式,只需要保证每个模块代码量小于程序Cache容量即可。处理器对于数据的读取同样可以采用类似方法,以达到充分利用数据Cache的目的。此方法不仅可以应用于AVS解码器,也可应用于AVS编码器,还可以应用于与之拥有类似结构的H. 264、MPEG、VC1等编解码算法。

- 基于VHDL的AVS环路滤波器设计(06-05)

- 双ARM7 SoC参考设计实现多电压AVS(12-09)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)