异步FIFO在FPGA与DSP通信中的运用

FIFO中,当写满约定的字符数时,将数据准备好信号置为有效,通知DSP可以取数据,当FIFO写满情况出现时,写满标志置为有效,阻止继续向FIFO中写入数据。当FIFO接收到DSP发来的启动数据发送信号且读使能信号均为有效时,FIFO就在DSP发来的读时钟的控制下,依次将数据放到16位读数据端,供DSP读龋

实现该FIFO的关键部分Verilog代码如下:

需要说明的是,在产生写满标志时,由于采用格雷码,写满标志判断的条件是:如果读写指针的最高两位不同,其余位相同,则为写满状态。为了说明简便,以4位格雷码表示深度为8的FIFO为例,当读指针指向第7个地址时,读指针为0100,此时若写指针指向第8个地址,则写指针为1100,此时两者仅最高位不同而其余位相同,但此时FIFO并不是处于写满状态,这与前文所叙述的用二进制码表示的读写指针判断方法是有区别的。当写操作写满一圈,第二次到达地址7时,此时的写指针为1000,可以看出,此时两者的最高两位不同,而其余位相同,这时FIFO真正处于写满状态。

2 DSP端数据接收

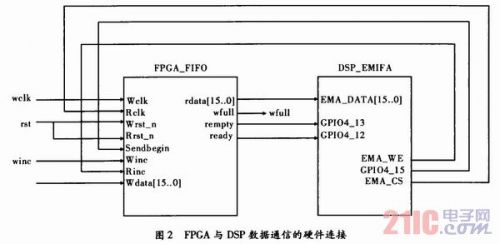

TI公司的TMS320C6000系列DSP均提供EMIFA接口,本文利用EMIFA接口实现FPGA向DSP传输数据,实现两者硬件连接的电路如图2所示。

其中,EMIFA的16位数据端与FIFO的Rdata端相连以便接收FPGA发来的数据,GPI04_13,GPI04_12,GPI04_15这3个通用IO口用来接收或输出相应的握手信号。EMA_WE与FIFO的读使能端相连,EMA_CS与FIFO的读时钟相连。

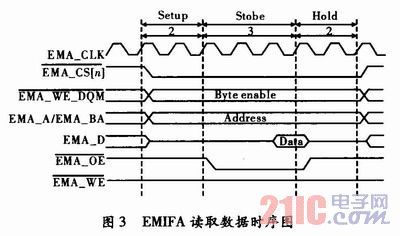

图3所示为DSP的EMIFA口读取数据的时序图,从图中可以看出,每一次读数据操作均以EMA_CS(EMIFA使能信号)下降沿开始,以EMA_CS的上升沿结束。同时,因为是读取操作,EMA_WE(EMA读写控制信号,低为写,高为读)始终为高电平,EMA_OE(EMA输出使能信号,低有效)在数据读取时刻为低电平。所以,将EMA_CS连至FIFO的Rclk端,恰好实现DSP读取一次数据,FIFO更新一个数据,而EMA_WE可作为FIFO的读使能信号。

3 仿真结果与结论

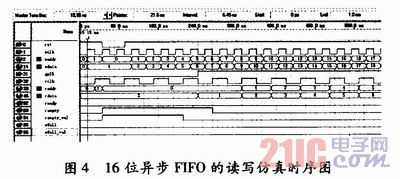

本文设计了数据宽度为16位,深度为2 048的FIFO,并使用Verilog语言编写了FIFO模块和与DSP的接口模块,利用该FIFO,FPGA实现了将数据1~65 535传递给DSP。在Quartus II软件下进行仿真得到的结果如图4所示。

由图4可以看出,在rst变为高电平以后,FPGA在Wclk的上升沿依次将数据写入FIFO中,写指针也从0开始逐次增1。在收到DSP发来的gp15(启动数据发送信号)有效后,在读时钟Rclk的上升沿,FPGA将数据从1开始逐次输出到Rada端,供DSP读取。DSP端在配置好EMIFA口后,编写的相应接收程序,正确接收到了从0~65 535这65 536个数据。

为实现FPGA与DSP之间的数据通信,本文提出了利用异步FIFO的方法,采用格雷码和两级D触发器同步的方法降低了亚稳态现象出现的概率。同时,给出了FPGA和DSP实现数据通信的硬件连接电路。经验证,利用异步FIFO的方法,能够稳定可靠地从FPGA中传输数据给DSP。

异步FIFO FPGA与DSP数据通信 DSP EMIFA 相关文章:

- 异步FIFO在DSP图像采集系统中的应用(10-15)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)