基于DSP TMS 3 2 0F2 8 1 2的智能接口板设计

0 引言

随着电子技术的发展,数字电路的集成度和性能有了非常大的提高,因此可以在单板上实现复杂的电路功能,本设计就是在TI公司高集成度的TMS320F2812处理器上设计外围接口电路,实现多路高速ARINC429接口、高速RS422接口、高速RS232接口,由于该款DSP的卓越性能,其接口板具有强大的多路接口通讯实时处理能力,同时由于该接口板的通讯接口都是标准接口,物理结构为PMC底板结构,所以具有一定的通用性。

1 系统设计

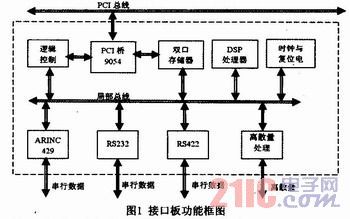

接口板采用TMS320F2812处理器,对串行数据的接收和发送采用智能控制方式,它通过一个512k(32k×16)双端口存储器(DPRAM)实现与主处理机的数据交互,双端口存储器与主处理机之间为PCI总线接口,物理连接方式为PMC标准插座。模块功能框图见图1。限于篇幅,本文主要介绍局部总线端电路设计,与主机接口端的PCI设计另有文章介绍。

接口板主要有如下的功能部分组成:

·处理器电路,数据处理器TMS320F2812,主频150MHz,集成128k字容量程序FLASH,18k字容量SARAM;

·双口RAM IDT70V27,容量为32k×16bit;

·时钟和复位电路,MAX791;

·10路全双工RS422串行接口电路,TL16C554;

·2路全双工RS232串行接口电路;

·4收2发ARINC429接口,DEI10l6A,BD429A;

·PCI总线接口电路PCI9054;

·逻辑控制电路XC95288XL;

·提供+5V转+15V,-15V电路,DCP020515DP,负载80mA。

1.1 处理器及存储电路

1.1.1 处理器

处理器选用TI公司的16位TMS320F2812芯片,主频可达到150MHz。主要特点如下:

·150MIPS运行速度;

·集成128k字容量程序FLASH,18k字容量SARAM;

·56路独立的可编程多路复用I/O引脚;

·锁相环(PLL)模块;

·3个32位定时器

·2个串行通信接口SCI;

·1个串行外设接口SPI;

·16路ADC(12bit);

·2路eCAN接口;

·3个可屏蔽中断;

·JTAG接口;

·哈佛结构。

本接口板在设计中用到TMS320F2812处理器的数据处理功能、存储器功能、通用IO功能、串行通信功能和JTAG接口。16位地址线A15~A0,16位数据线D15~D0。

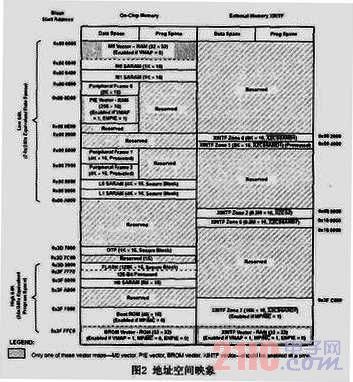

TMS320F2812处理器地址空间映像如图2所示。

该接口板地址分配如表1所示。

1.1.2 存储电路

在实时系统中,串行数据的采集及交换是影响系统开销的瓶颈之一,在这类系统中,数据交换要求的通讯速率往往很高。传统的并行接口和串行接口设计无论在通信速率,还是在可靠性方面都不易满足要求。而双端口RAM则是一个较好的实现方案。双端口RAM的优点是通讯速度快,实时性强,接口比较简单,两边CPU都可主动进行数据传输,因而可在这类设计中广泛应用;其缺点是成本高,需要克服竞争现象。

双端口RAM芯片有两套完全独立的数据线、地址线和读写控制线,因而可使两个处理器分时独立访问其内部RAM资源。由于两个CPU同时访问时的仲裁逻辑电路全部集成在双端口RAM内部,因而需要实际设计的电路比较简单。双端口RAM内一般都有一个总线抢占优先级比较器,只要双CPU不同时访问同一存储单元,那么较先送出地址的CPU将拥有该单元的本次访问优先权,而另一个CPU的地址与读写信号将被屏蔽掉,同时通过"busy"引脚告知该CPU以使之根据需要对该单元重新访问或撤销访问。

共享存储器选用双口内存IDT7027,存储容量为32k×16bit。共享存储器具有两组独立的地址、控制、I/O引脚,允许从任一组引脚发出的信号对内存中的任何位置进行读或写的异步访问。双口内存IDT7027具有防止双口竞争的功能,该功能可以免去为避免双口竞争增加的硬件逻辑,通过使用芯片上的信号量可以获得芯片的控制权,只有获权的一组引脚上的信号才能访问内存,另外通过信号量的使用还可以将双口内存划分为大小不同的区。

在此模块设计中,双口存储器一边由DSP处理器控制,另一边由PCI总线进行控制,而芯片本身自带的BUSY通过逻辑设计接READY来实现双口存储器产生竞争时的应答。

·双口存储器读操作访问

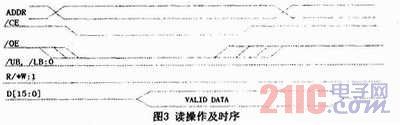

双口存储器的读操作时序如图3所示,/CE为读写数据操作的片选信号,低电平有效;/OE为输出控制信号,由系统读信号控制,低电平有效;/UB、/LB是高/低字节有效控制信号,低电平有效,设计中将这两信号下拉;R/*W信号在读操作中保持高电平。

·双口

智能接口板 DSP TMS 3 2 0F2 8 1 相关文章:

- 基于DSP TMS320F2812的智能接口板设计(01-25)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)