TMS320C54X DSP实现UART的技术

TMS320C54x DSP的外设没有集成UJART串口,可以通过两种途径来实现TMS320C54X的LJART串口通信功能。一是通过软件的方法。二是采用外部接口芯片组,完成RS232信号的接收和发送,并以DSP容易快速访问的方式与DSP接口。

1 采用软件模拟

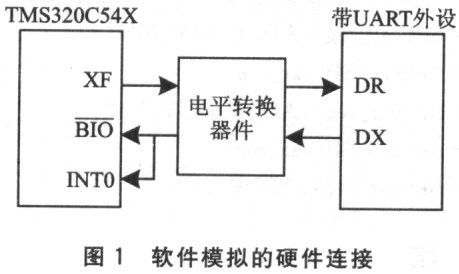

TMS320C54x DSP软件模拟实现LJART无需额外硬件开销,仅需通用I/(BIO和XF)、外部中断INTO以及一个定时器就可实现,硬件连接如图l所示。

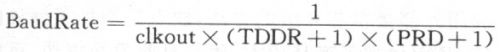

图l中,XF引脚用于发送数据,BIO脚和INTO脚用于接收数据。此方法可以模拟半双工通信与全双工通信。软件模拟IJART技术允许用户设置:数据位数(1~16)、奇偶校验(奇校验或偶校验)或无奇偶校验、停止位(1~2)和波特率。每秒传输比特数计算公式为:

改变寄存器TDDR和PRD的设置值,可以获得不同的波特率。BaudRate最大值是:

其中,clkfreq是DSP系统时钟,#cycles是子程序执行周期,bit是完成UART功能限定条件(1/2或1)。

另外,需要两个存储单元分别用作UART状态寄存器和计数器,以便控制软件完成接收与发送任务。

1.1 接收功能

要正确接收数据流,首先要检测起始位。由于百BIO和INTO连在一起,一旦低电平有效则启动INTO中断。首次响应中断,定时器设置定时周期为1/2码元宽度,以便保证在起始位中间位置定时中断采样BIO引脚。如果采样电平为高,起始位就是虚假信号,定时器立即停止定时并退出子程序。如果为低,则认为检测到起始位,关闭外部中断INTO以免数据流中的O再被误认为是起始位。接收后续数据时,每次定时器没置定时周期为一个码元宽度,保证在码元中间采样,从而减少误码。当收到若干个(数据位数可根据需要设定为1~16)数据后,再检测停止位和奇偶校验位。若数据接收正确,则格式化输出数据(去掉起始位、停止位和奇偶校验位)。同时计数器清零,复位RCV(接收标志位.在LJART状态寄存器中设定)标志位,并开中断为下一次检测数据流的起始位做好准备。

1.2 发送功能

一旦发送数据,并且发送子程序被调用,必须先将发送数据格式化(加上起始位、停止位和奇偶校验位)存在某个存储单元以备发送。然后,检测TX位是否被置位(即有无数据正在发送)。若是,则循环等待直到TX(发送标志位,在UART状态寄存器中设定)被复位为止。要知道何时开始发送下一个数据,需要定时器定时中断来控制,同时还需要一个发送计数器控制程序流程。由于发送和接收是独立进行的,它们共用唯一的一个定时器,如果UART在接收数据过程中定时器突然被发送功能占用,则必然会破坏数据。发送数据前必须检测RCU标志位,确认没有正在接收数据后才能开始发送数据,否则发送程序等待。因此,准确来讲,这种发送接收方式只是一种半双工方式,发送和接收不能同时进行。如果要实现全双工通信,则无论是否正在接收数据,发送都延迟一段时间等待下一次接收,然后与其同步进行。

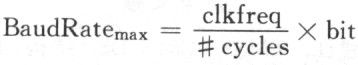

2 增加专用UART接口

利用TLl6C550C和MAX3238分别实现协议转换和电平转换。增加专用UART接口的硬件框图如图2所示。

主机通过并行方式访问TIJl6C550C的寄存器,寄存器的设定将控制其内部的控制逻辑模块,实现对其工作方式的设定(如波特率、校验位等),同时,访问寄存器也可以实现对数据的操作(读取和写入数据)。RS232数据接口可大致分为三部分;接收模块、发送模块和Modem控制逻辑。接收模块将从SIN引脚输入的串行数据,按照规定格式取出其数据部分并作校验,数据接收部分被送入接收寄存器或接收FIFO中,校验的结果反映在状态位上。发送模块将发送寄存器或发送FIF0中的数据按照规定格式加入起始位、停止位和校验位,并以RS232的串行方式发送至SOUT引脚。Modem控制逻辑通过接收和发送引脚信号,实现对收发操作的控制。

对DSP而言,TLl6C550C是一系列寄存器,它们映射在I/0空间中,通过译码电路使它的起始地址为0x4000,那么对其操作即是对其某段地址的I/O进行访问。LIART的每个寄存器都是8位的,大多数寄存器只能工作在一种模式下(读或写)。

2.1 串行传输

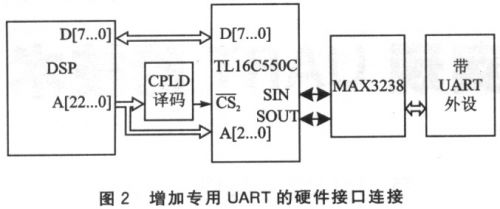

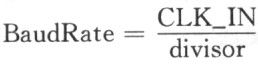

异步串行数据格式的设置通过线路控制寄存器(LCR)来完成的。除了数据格式外,另外一个指标是波特率,它是通过除数寄存器来设置的,实际的波特率为输入时钟信号进行分频后获得,其公式如下:

2.2 数据接收

从SIN输入的数据首先进入接收移位寄存器(RSR),一个字符接收完成后,数据移人接收缓冲寄存器(RBR)。RBR实际是一个16字节的FIFO,当中断设置时,UART会根据FIFO中接收数据的数目产生中断,主机设备从RBR中读取数据后,中断会自动清除。

2.3 数据发送

DSP UART TMS320C54X 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)