基于DSP的高阶COSTAS锁相环的设计

COSTAS环是一种闭环自适应系统,用于提取相干载波。本文主要介绍了一种用于载波同步的高阶COSTAS环路,用于完成MPSK的相干解调中的载波同步。本文提出了一种便于软件实现的COSTAS环路的简化结构,用于完成8PSK的载波同步,并详细讨论了采取数字信号处理器(DSP)编程实现COSTAS环路的一些问题。

关键词:COSTAS环, DSP, MPSK, 载波同步

1. 引言

MPSK调制是应用最为广泛的数字调制方式之一。按照信号检测理论,对MPSK调制信号的平均误码率最小的最佳接收方式为采用锁相环路的相干接收方式。但是,MPSK调制信号是抑制载波的信号,不能用常规的锁相环或窄带滤波器直接提取参考载波。而且不同于一些相位连续的调制信号,其载波相位变化只能取有限的几个离散值,说明调制信号中包含了参考载波的相位信息。可以通过非线性处理,消除信号中的调制信息,恢复调制信号中的隐含的载波信号,从而完成信号的相干解调。目前,常用的MPSK载波恢复的方法包括:平方环法,锁相环法等。本文中,作者设计了新型的高阶COSTAS环,它具有可靠、捕捉带宽大、能快速实现同步的优点。

2. 高阶COSTAS环路的工作原理和结构

Costas在1956年首先提出采用同相-正交环来恢复载波信号。随后,Riter等人证明跟踪低信噪比的抑制载波信号的最佳装置为COSTAS环及平方环。COSTAS环路是一种闭环自动调整系统,传统的模拟COSTAS环路因为同相支路与正交支路的不平衡性从而使环路的性能受到一定影响,并且模拟电路存在直流零点漂移、调试困难的缺点,而全数字COSTAS环可以避免以上缺点,而且基于软件无线电原理的COSTAS环路具有很强的兼容性。

2.1 普通COSTAS环路的工作原理和设计

2.1.1 COSTAS环路的一般原理

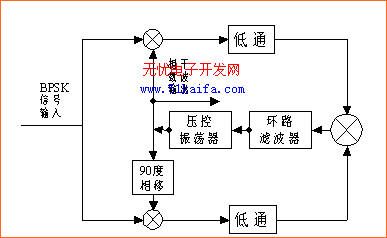

COSTAS环路包括鉴相器、环路滤波器、压控振荡器。鉴相器是一个简单的乘法器。LF(环路滤波器)在COSTAS环路中不仅能起到低通滤波器的作用,并决定了COSTAS环路的性能参数。由于理想二阶有源环路滤波器性能远优于其它环路,锁定时稳态相差为0,同步带大,本文采用理想二阶环路,其数字化原理图如图1所示。

图1 COSTAS基本原理

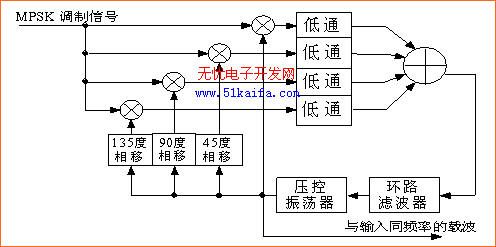

2.2 多相信号中提取载波

对于BPSK有两个相位,可用上述方法来提取载波。但是常用的MPSK有M个相点,不能采用图1的COSTAS环路来提取载波,必须采用多相COSTAS环。

图2 四相PSK信号COSTAS环原理框图

3. 高阶COSTAS环路的DSP算法优化

从上面M=8的高阶锁相环的结构来看,8PSK信号进入高阶COSTAS环路,需要采用DSP实现八路鉴相器,八路低通滤波器(滤掉倍频分量,得到低频分量)和压控振荡器,计算量是非常庞大的。如何进行资源合理配置、达到DSP实时处理是载波恢复的难点,因此需要对DSP程序的优化作深入的研究。

在用C语言进行DSP软件开发时,一般先在PC机上对算法进行仿真,再将C语言移植到DSP平台中。按照开发的顺序,相应的优化工作也包括两部分:一是仿真环境中的优化,二是DSP目标环境的进一步优化。下面结合TI公司的TMS320C64x系列DSP的C编译器,讨论在MPSK的相干解调中的具体优化工作。

3.1 SIN/COS函数的查表算法

为了提高算法的实现效率,介绍运行时计算的时间开销,应尽可能把一些运行时计算的参数做成查找表或常数数值。这不仅适用于一些比较规整的参数表,对于一些并不规整的运行时的计算,例如上下变频和VCO中,用到与载波相乘的SIN/COS的计算,可以采用写成数组,用查表来实现。

3.2 运算的流水处理

DSP的CPU多采用流水线结构。DSP的大多数指令为单周期指令,而跳转类指令却通常要耗费较多的机器周期。可以将多重循环拆开,减少对外层循环次数进行控制转移的时间,充分利用优化器构成的流水线。

3.3 CIC梳状滤波器的使用

利用CIC滤波器代替低通滤波器,达到减少定点乘法和加法运算的目的,解决了单片C6416资源不足的问题。例如:本文中载波速率为4800kHz,采样率为230.4kHz,鉴相器输出的高频频率为9600kHz,采用48阶CIC可以将9600kHz的频率分量滤掉。由于在 的位置,因此滤除效果非常好,远大于 。CIC滤波器每项系数都是1,利用加法运算可以实现需要大量乘法和加法运算的功能,减少对DSP片内资源的使用。

3.4数据传输的EDMA方式

在调制解调过程中,DSP和外部之间存在大量数据的交换,这部分的优化工作影响系统性能。C64x支持EDMA,EDMA是增强型DMA,是一种在没有CPU介入情况下的访问存储器的方式,即由EDMA控制器控制数据在L2内存/缓存和片内集成外设及片外设备之间的传输,而同时CPU可以并行的执行其它指令。EDMA

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)