一种DSP的远程多加载方案设计

引言

芯片的烧写与自加载是一个DSP系统能够顺利运行的基本条件。在DSP加载技术方面已经有大量文献和工作成果,比较好地解决了DSP自加载方面的许多基本问题。而传统的烧写/加载方案在调试、更新程序时需要反复外接仿真器,配置跳线,并且只能加载运行指定地址空间上的工程。这些对处于安装调试阶段的系统影响不大,但在诸如航天设备、大型机械或其他恶劣环境中工作,难以直接进行仿真器连接的DSP系统中,无法采用普通的烧写/加载方案对其进行更新和调试。

通过分析DSP系统加载原理,提出了一种基于TI公司C6x芯片的远程多加载DSP系统设计。该系统由通信芯片、DSP、外部动态存储器、外部闪存(Flash)共同组成,具备远程烧写、程序选择加载功能。系统程序更新时也具备很高的安全性,即使烧写过程中断电,下次上电后仍然可以继续烧入、运行新的工程。

1 系统结构

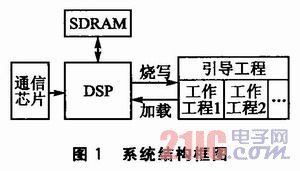

为了满足功能设计需求,加载与烧写系统除了包括DSP系统运行必需的DSP芯片之外,还需要连接外部动态存储器(SDRAM)、可擦除存储器(Flash)、通信芯片等。系统结构如图1所示。其中,通信芯片负责与远程控制端进行数据交换,SDRAM中存放DSP工作用代码和数据,而负责引导实际工作工程的"引导工程"和负责实际信息处理任务的"工作工程"代码数据分别存放于不同的Flash空间。

2 实现方案

首先简要说明C6x系列DSP的普通二次加载工程的引导原理。自加载模式的DSP上电初始时,会从CE1空间起始地址(0x90000000)开始拷贝一定长度(C671x系列为1 KB)的数据到内部存储器0地址,并从0地址开始执行程序。由于拷贝数据长度有限,通常情况下一个长度大于1 KB的自加载工程需要进行二次加载操作,因此该工程必须包含一个长度小于1 KB的Bootloader模块,该模块由进行二次加载数据搬移操作的代码构成。工程编译完成后,Bootloader模块被烧写在Flash最开头的1 KB地址空间内,系统上电复位后由DSP自动搬运到0~1 KB地址空间内执行(第一次加载),并由该模块进行其他数据段的数据搬移(第二次加载)。在数据搬移结束后Bootloader模块将PC指针跳转到_c_int00地址段,并最终进入主函数,开始整个工程的运行。整个自加载过程如图2所示。

显然,只有存放在DSP CE1空间最前端的数据才能被自动加载和运行。为了使系统上电时刻就具备通信、烧写和多引导功能,需要将具备上述功能的引导工程存放在CE1基地址开始的空间。

DSP多引导技术正是在普通DSP系统的加载技术基础上发展而来的,将具备引导、通信、烧写、存储器检纠错功能的工程作为引导工程独立存储在DSP CE1空间,由DSP自动加载运行;而将具备不同功能的应用程序代码分别存储在其他存储器,等待引导工程根据功能需要去加载。

引导工程由DSP自动运行,随后根据远程指令或按预定程序流程的执行通信、更新工作工程代码,或搬运并运行存储在其他空间工作工程内的Bootloader段,从而引导不同功能的工作工程运行。借助这种工程分离运行技术,可以通过远程端或自动对空间电子设备存储器中的代码进行更新、检纠错和加载操作,甚至进行多个工作工程的切换以满足不同应用背景下的功能需求;即使在更新或切换过程中出现故障,系统复位后仍可回到正常工作的引导工程中进行系统维护或重新更新,具备防烧写功能。

2.1 引导工程设计

引导工程是负责与远程控制端通信,获取工作工程代码并完成烧写、引导工作工程加载运行的程序。引导工程需要具备自加载、上传校验数据、烧写引导等功能。

2.1.1 自加载功能

引导工程采用普通工程的加载/烧写方式,需要在产品生产完成后以仿真器模式进行烧写固化。由于引导工程具备需要通信、烧写等功能,其数据长度一般来说会超出1KB的DSP自动搬移长度限制,所以系统中的引导工程首先需要设计成一个具有二次加载能力的工程,并烧写在DSP存储器CE1空间的最前端,确保DSP在自动引导时首先加载和运行的是引导工程。

在设计引导工程自加载功能时,与普通二次加载工程相比有所不同:

①程序存储地址要加以限制,避免占用工作工程空间;

②引导工程的Bootloader必须放置在CE1空间的最开头1 KB内,使DSP能够在上电时自动加载运行。

2.1.2 通信功能

通信模块主要由通信芯片和通信控制逻辑组成,负责完成远程控制端与DSP之间的通信。根据不同应用场合,可以选择不同的通信芯片与链路协议。下面主要考虑应用层协议设计。

(1)数据上传与校验

按照参考文献中的方法,为了将工作工程在线烧写到Flash存

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)