基于DSP Builder数字信号处理器的FPGA设计

的系统仿真是针对算法实现的,与目标器件和硬件系统没有关系,其仿真结果并不能精确反映电路的全部硬件特性,因此,需要对设计进行时序仿真。

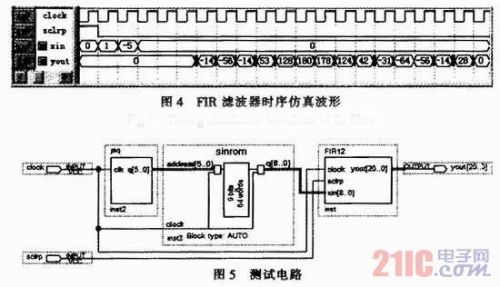

在QuartusⅡ环境中,打开DSP Builder建立的QuartusⅡ工程文件,对上述的VHDL代码进行时序仿真。图4为在OuartusⅡ7.O环境下FIR数字滤波器时序仿真图。图4中clock为系统时钟,sclrp为清零信号,xin为输入数据,yout为滤波器的输出结果。

由式(2)知:若xin{1,-5},h(n)={-22,-33,-13,41,108,154,154,108,41,-13,-33,-22},则滤波器的输出yout的理论结果为:yout=xinh(n)={-14,-56,-14,53,128,180,178,124,42,-31,-64,-56,-14,28}。可见,所设计的FIR数字滤波器在QuarmsII 7.0中进行时序仿真得到的输出结果和理论上计算得到的结果是完全一致的。

3 实际硬件测试

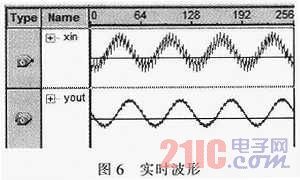

只进行工程软件仿真远远不够,还必须进行硬件实时测试。在硬件实际运行时,可以从外部信号源接入器件内部或者在其内部存储正弦波数据。这里采用后者,即在顶层文件中引入LPM_ROM宏模块,在其中存入频率分别为0.5和8 kHz2个正弦波迭加信号数据的.hex文件.FIR滤波器模块直接从ROM中读取数据,测试电路如图5所示。

在QuartusⅡ环境中,对测试电路进行编译,下载到cyclone系列EP1C12Q240C8器件后,就可以对硬件进行测试。采用Ahem公司的Signal-TapⅡ嵌入式逻辑分析仪进行芯片测试,用户无需外接专用仪器,就可以通过FPGA器件内部所有信号和节点的捕获对系统故障进行分析和判断,而又不影响原硬件系统的正常工作。

经嵌入式逻辑分析仪得到的实时波形如图6所示。实际测试发现,经过设计的低通滤波器后,高频信号被滤除,只有低频信号输出,滤波效果满足系统要求。需要注意的是,SignalTapⅡ嵌入式逻辑分析需工作在JTAG方式,在调试完成后,需将SignalTapⅡ移除设计,以免浪费资源。

4 结束语

由以上设计过程可知,基于Matlab/Simulink/DSP Builder/OuartusⅡ的设计流程,可以帮助设计者完成基于FPGA的数字信号处理系统设计。使用相对独立功能的电路模块和子系统进行模块化的设计,避免了繁琐的VHDL语言编程;设计者只要对DSP Builder模块库中相应模块的基本参数进行简单设置,而不需要对各模块具体的实现过程进行详细了解,甚至不需要了解FPGA本身和硬件描述语言,极大缩短了开发周期。而且随着技术的发展,FPGA的性能越来越高,价格则逐步降低,芯片的处理速度更快,片内资源更大,这将给FPGA在信号处理领域的应用提供更为广阔的空间。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)