音频信号采集与AGC算法的DSP设计方案

过去,对大音频信号采用限幅方式,即对大信号进行限幅输出,小信号不予处理。这样,仍然存在音频信号过小时,用户自行调节音量,也会影响用户的收听效果。随着电子技术,计算机技术和通信技术的迅猛发展,数字信号处理技术已广泛地深入到人们生活等各个领域。其中语音处理是数字信号处理最活跃的研究方向之一,在IP电话和多媒体通信中得到广泛应用。

语音处理可采用通用数字信号处理器DSP和现场可编程门阵列(FPGA) 实现,其中DSP实现方法具有实现简便、程序可移植行强、处理速度快等优点,特别是TI公司TMS320C54X系列在音频处理方面有很好的性价比,能够解决复杂的算法设计和满足系统的实时性要求,在许多领域得到广泛应用。在DSP的基础上对音频信号做AGC算法处理可以使输出电平保持在一定范围内,能够解决不同节目音频不均衡等问题。

电台等由于其自办频道的广告、新闻、广播剧、歌曲和转播节目等音频信号电平大小不一,导致节目播出时,音频信号忽大忽小,严重影响用户的收听效果。在转播时,由于传输距离等原因,在信号的输出端也存在信号大小不一的现象。

音频信号采集

TI公司DSP芯片TMS320VC5402具有独特的6总线哈佛结构,使其能够6条流水线同时工作,工作频率达到100MHz。利用VC5402的2个多通道缓冲串行口(McBSP0和McBSP1)来实现与AIC23的无缝连接。VC5402的多通道带缓冲的串行口在标准串口的基础上加了一个2K的缓冲区。每次串口发送数据时,CPU自动将发送缓冲中的数据送出;而当接收数据时,CPU自动将收到的数据写入接收缓存。在自动缓冲方式下,不需每传送一个字就发一次中断,而是每通过一次缓冲器的边界,才产生中断至CPU,从而减少频繁中断对CPU的影响。

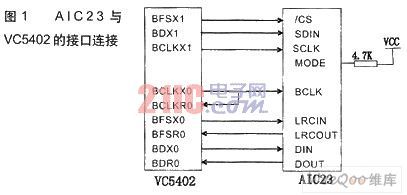

音频芯片采用TLV320 AIC23,它是TI公司的一款高性能立体声音频A/D,D/A放大电路。AIC23的模数转换和数模转换部件高度集成在芯片内部,采用了先进的过采样技术。AIC23的外部硬件接口分为模拟口和数字口。模拟口是用来输入输出音频信号的,支持线路输入和麦克风输入;有两组数字接口,其一是由/CS、SDIN、SCLK和MODE构成的数字控制接口。AIC23是一块可编程的音频芯片,通过数字控制口将芯片的控制字写入AIC23内部的寄存器,如采样率设置,工作方式设置等,共有12个寄存器。音频控制口与DSP的通信主要由多通道缓冲串行口McBSP1来实现。TLV320AIC23B pdf datasheet AIC23通过数字音频口与DSP的McBSP0完成数据的通信,DSP做主机,AIC23做从机。主机提供发送时钟信号BCLKX0和发送帧同步信号BFSX0。在这种工作方式下,接收时种信号BCLKR0和接收帧同步信号BFSR0实际上都是由主机提供的。图1是AIC23与VC5402的接口连接。

AIC23的数字音频接口支持S(通用音顿格式)模式,也支持DSP模式(专与TIDSP连接模式),在此采用DSP模式。DSP模式工作时,它的帧宽度可以为一个bit长。

图2是音频信号采集的具体电路图。

电路的设计和布线是信号采集过程中一个很重要的环节,它的效果直接关系到后期信号处理的质量。对于DSP达类高速器件,外部晶体经过内部的PLL倍频以后可达上百兆。这就要求信号线走等长线和绘制多层电路板来消除电磁干扰和信号的反射。在两层板的前提下,可以采取顶层与底层走交叉线、尽量加宽电源线和地线的宽度、电源线成"树杈型"、模拟区和数字区分开等原则,可以达到比较好的效果。

音频AGC算法的实现

AGC算法

使放大电路的增益随信号强度的变化而自动调整的控制方法,就是AGC-自动增益控制。实现AGC可以是硬件电路,即AGC闭环电子电路,也可以是软件算法。本文主要讨论用软件算法来实现音频信号的AGC。

音频AGC是音频自动增益控制算法,更为准确的说是峰值自动增益控制算法,是一种根据输入音频信号水平自动动态地调整增益的机制。当音量(无论是捕捉到的音量还是再现的音量)超过某一门限值,信号就会被限幅。限幅指的是音频设备的输出不再随着输入而变化,输出实质上变成了最大音量位置上的一条水平线;当检测到音频增益达到了某一门限时,它会自动减小增益来避免限幅的发生。另一方面,如果捕捉到的音量太低时,系统将自动提高增益。当然,增益的调整不会使音量超过用户在调节向导中设置的值。图3是音频AGC算法的结构框图。

AGC算法的实现过程

首先从串口获取音频数据,它是16位的整型数,一般来说,这些数都是比较小的,通过AGC算法将输入的音频数据投影在一个固定区间内,从而使得不论输入的数据点数值大小都会等比例地向这个空间映射。一方面将获得的音频数据最大值与原来的峰值进行比较,如果有新的峰值出现

- 音频信号采集与AGC算法的DSP实现方案(05-25)

- TMS320C6727的音频采集处理回放系统设计(01-05)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)