基于DSP和IPM的变频调速系统的硬件设计

时间:11-25

来源:作者:刘永红 陕西普声电气有限公司

点击:

硬件设计要点

根据笔者设计该系统的经验,硬件设计应注意以下方面,以提高系统抗干扰性,使之在强干扰的现场工业环境中能可靠稳定运行。

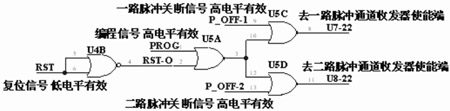

·虽然DIP-IPM模块可由DSP直接驱动,但实际调试时发现,在上电及对DSP进行flash编程过程中,DSP的引脚有时会出现不确定状态,产生干扰脉冲导致IPM的上、下臂IGBT直通引起短路保护动作。故我们在DSP到IPM的两组触发脉冲通道中分别加了一个八通道、双电源3态门转换收发芯片74LVC4245,该芯片的输出使能端由一个简单的逻辑门电路控制,如图3所示。以确保在上电及对DSP进行flash编程时不会有干扰脉冲误触发IPM。

·为防止信号振荡,应在各输入端加RC退耦电路。对两组触发脉冲来说,RC电路一来可滤掉干扰脉冲,二来还可限制输入脉冲的最小脉宽。RC容量的选择要和PWM的载波频率匹配,使得既能滤掉干扰信号,又不对触发脉冲造成畸变。因为DIP-IPM输入部分IC内置2.5KΩ(min)下拉电阻,故RC中R阻值的选择应注意使分压后的信号值满足DIP-IPM的输入电平阈值要求。

·DIP-IPM还有一个很实用的功能:短路保护。在本系统的软件调试过程中,该功能多次发挥作用,可靠地保护了模块,使本系统样机调试过程中IPM模块无一损坏。但要使该功能可靠发挥作用,应注意以下两点:

1)外部电流检测电阻的信号回路必须设置RC滤波电路,以免短路保护误动作。RC时间常数的选择要考虑IGBT的硬中断能力,一般推荐为1.5~2μS,最大不超过6μS。时间常数过短可能引起短路保护误动作,过长则可能超出IPM模块的耐受能力,不能有效保护IPM模块。

2)外部电流检测电阻应为无感电阻,该电阻及其信号引线到IPM模块对应引脚的布线应尽可能短,以免由引线电感干扰引起短路保护误动作。

·PCB布板时应注意采取以下抗干扰措施:

1)强电(功率部分)和弱电(控制部分)从区域上分开。

2)数字地(控制地)和模拟地(功率地)分开布局,只能在一点相接。一定要注意避免功率地线上的电流流经控制地线,以免引入地线干扰。

3)PCB上IPM模块相邻触发脉冲引脚间可开槽,避免相互干扰。

4)电流检测电阻及其信号线、触发脉冲信号及所有电容到IPM模块的布线要尽可能短,尽量降低其引线电感引起的干扰。

结语:

该系统已批量生产上千台,投入现场连续运行三年多。实际运行表明,该系统运行稳定,工作良好。可以预计,DSP+IPM模式将是紧凑型变频调速系统的发展方向之一。

参考文献:

[1] TMS320LF2407A DSP controller,TI,2002

[2] DIP-IPM version3 应用技术资料,三菱电机株式会社,2003

根据笔者设计该系统的经验,硬件设计应注意以下方面,以提高系统抗干扰性,使之在强干扰的现场工业环境中能可靠稳定运行。

·虽然DIP-IPM模块可由DSP直接驱动,但实际调试时发现,在上电及对DSP进行flash编程过程中,DSP的引脚有时会出现不确定状态,产生干扰脉冲导致IPM的上、下臂IGBT直通引起短路保护动作。故我们在DSP到IPM的两组触发脉冲通道中分别加了一个八通道、双电源3态门转换收发芯片74LVC4245,该芯片的输出使能端由一个简单的逻辑门电路控制,如图3所示。以确保在上电及对DSP进行flash编程时不会有干扰脉冲误触发IPM。

·为防止信号振荡,应在各输入端加RC退耦电路。对两组触发脉冲来说,RC电路一来可滤掉干扰脉冲,二来还可限制输入脉冲的最小脉宽。RC容量的选择要和PWM的载波频率匹配,使得既能滤掉干扰信号,又不对触发脉冲造成畸变。因为DIP-IPM输入部分IC内置2.5KΩ(min)下拉电阻,故RC中R阻值的选择应注意使分压后的信号值满足DIP-IPM的输入电平阈值要求。

·DIP-IPM还有一个很实用的功能:短路保护。在本系统的软件调试过程中,该功能多次发挥作用,可靠地保护了模块,使本系统样机调试过程中IPM模块无一损坏。但要使该功能可靠发挥作用,应注意以下两点:

1)外部电流检测电阻的信号回路必须设置RC滤波电路,以免短路保护误动作。RC时间常数的选择要考虑IGBT的硬中断能力,一般推荐为1.5~2μS,最大不超过6μS。时间常数过短可能引起短路保护误动作,过长则可能超出IPM模块的耐受能力,不能有效保护IPM模块。

2)外部电流检测电阻应为无感电阻,该电阻及其信号引线到IPM模块对应引脚的布线应尽可能短,以免由引线电感干扰引起短路保护误动作。

·PCB布板时应注意采取以下抗干扰措施:

1)强电(功率部分)和弱电(控制部分)从区域上分开。

2)数字地(控制地)和模拟地(功率地)分开布局,只能在一点相接。一定要注意避免功率地线上的电流流经控制地线,以免引入地线干扰。

3)PCB上IPM模块相邻触发脉冲引脚间可开槽,避免相互干扰。

4)电流检测电阻及其信号线、触发脉冲信号及所有电容到IPM模块的布线要尽可能短,尽量降低其引线电感引起的干扰。

结语:

该系统已批量生产上千台,投入现场连续运行三年多。实际运行表明,该系统运行稳定,工作良好。可以预计,DSP+IPM模式将是紧凑型变频调速系统的发展方向之一。

参考文献:

[1] TMS320LF2407A DSP controller,TI,2002

[2] DIP-IPM version3 应用技术资料,三菱电机株式会社,2003

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP的混合悬浮控制系统的硬件设计(01-13)