基于MCU+DSP的运动控制硬件平台设计

⑤4路数字信号输入, 包括伺服准备好、左极限、右极限和零位信号;

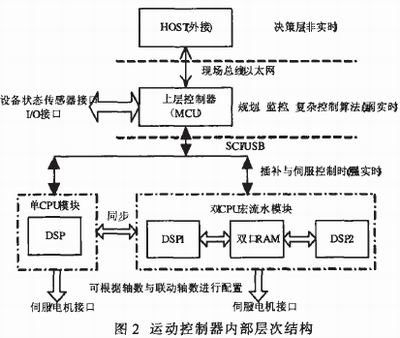

上述接口电路也可以联接步进电机。运动控制器的内部层次结构如图2 所示:

上层控制器处理复杂控制算法及弱实时任务, 下层控制器处理插补与伺服控制等强实时任务。两个DSP构成双DSP流水线模块, 并行处理复杂实时控制任务。

运动控制系统研究硬件平台设计

主芯片选型

MCU与DSP芯片选型的原则是适用与广泛性原则, 选用的芯片适用于开放式控制器设计并有广泛的硬件与软件资源。三星公司S3C2410A芯片采用ARM920T内核, 主频高达266MHz, 支持WinCE与Linux及μC/OS- II实时操作系统, 可扩展的地址空间1G, 并配有中断、AD、UART、GPIO、触摸屏和TFT接口等片上外设; 德洲仪器公司的TMS320F2812DSP 芯片的主频150MHz, 支持DSP/BIOS和μC/OS- II 实时操作系统, 可扩展的地址空间为1M, 并配有中断、AD、串行接口、事件管理器等片上外设。这两种CPU中,S3C2410A主要用于控制系统管理、监控和复杂控制算法的实现, DSP主要用于伺服电机接口和反馈、滤波等强实时控制算法的实现。

硬件系统配置

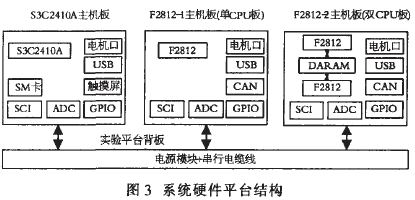

整个研究平台硬件配置了三块主机板和一个背板, 其结构如图3 所示:

三块主机板可以单独使用, 也可以组合使用, 它提供了MCU和DSP及双DSP的硬件平台S3C2410A。主机板的USB是Host, 另两块板的USB是Device配置, 另外, S3C2410A主机板和F2812主机板还通过背板有串口通信、GPIO及中断沟通, 可以组合成一个以S3C2410A主机板为上位机, F2812 - 1和F2812- 2主机板为下位机的双层结构, S3C2410A主机板处理弱实时任务, DSP处理强实时任务;

弱实时任务包括系统监控、模糊与神经网络等复杂控制算法, 强实时任务包括插补计算、数字滤波和PID控制等算法。由此来验证MCU和DSP环境中的算法可行性。

CPU 扩展与外设配置

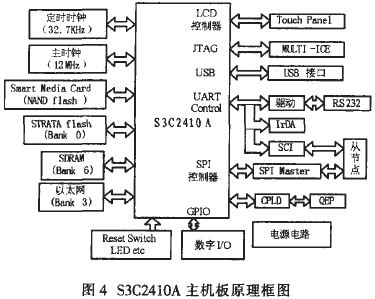

针对本系统设计要求, S3C2410A主机板原理框图如图4所示。选用两片HY58V561620CT- H, 构成16M×32位RAM空间; 选用两片E28F128J3A150, 构成16M×32 位Flash空间; CPLD选用XC9536, 用于GPIO地址译码和QEP接口的实现, 选用DAC8534A串行16位DAC扩展数模转换接口, 采用CS8900A 以太网芯片扩展网络接口。

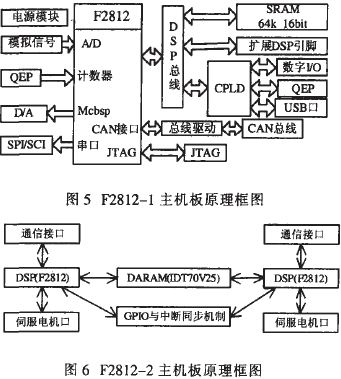

F2812-1主机板原理框图如图5所示, 选用IS61V5126, 扩展256KROM空间, 选用AM29LV800BT扩展512KFlash, 选用XC95144XL进行GPIO地址译码, 选用AN2131Q作USB Device的扩展, 在McBSP串口上扩展16位DAC8534A用于伺服的速度与力矩控制。特别的, F2812提供了完善的伺服电机接口, 它有两个事件管理器, 每个事件管理器包括两个通用计数器, 三个比较/PWM单元, 三个捕捉单元, QEP通道。PWM和通用计数器配合可用作伺服控制器的位置控制模式输入, QEP通道可用作伺服电机的位置编码器脉冲输入, 执行器终端的编码器信号通过CPLD扩展QEP输入。

F2812-2主机板原理框图如图6所示, 为了验证多电机的并行控制算法, 在F2812-1主机板的基础上, 用双口RAMIDT70V25将两个CPU联接起来, 形成了一个对称结构。按目前板上的电机接口配置, 每块板可接两路全闭环伺服电机, F2812-2主机板可接四路全闭环的伺服电机。

结论

选用S3C2410A和F2812作运动控制系统的嵌入硬件研究平台, 组成一个多CPU的双层控制器结构,既可以单独进行单MCU和DSP环境中的运动控制算法研究, 又可以进行多CPU平行模式的复杂运动控制系统研究。系统简练、可靠, 符合运动控制器的开放式、可重构和网络化的发展方向。

本文作者创新点:针对嵌入式运动控制器发展趋势,设计实现了一个开放式、可重构、多CPU的运动控制器硬件平台, 该平台可用于复杂运动控制系统的研究。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)