DSP与PC机的无线交换调制模块设计

时间:09-17

来源:

点击:

4.2.1 硬件连接图

调制的硬件电路如图3所示。TMS320C5402的IOSTRB和IS相或后作为CA3338的片选信号,通过数据总线将数据送到CA3338中,D/A转换后模拟信号经过运算放大器后输出。

4.2.2 DSP调制程序设计

原始数据在DSP中进行FTSK调制,它是通过DSP的软件编程利用DDS(数字合成频率)的原理实现的。

1 实现方法。DDS(直接数字频率合成)技术是一种把一系列数字量形式的信号通过DAC转换成模拟量形式的信号的合成技术。目前使用最广泛的一种DDS方式是利用高速存储器作查寻表,然后通过高速DAC产生已经用数字形式存入的正弦波。在本系统中,首先,在DSP内部ROM开辟一段存储空间作为一个周期的正弦波抽样点存储器。通过软件对该存储器进行相位一幅值的转换,从而在给定的时间确定相应的输出幅值。发送一个周期的正弦波流程图如图4所示。

2 4FTSK信号的产生及输出。4FTSK信号包含4个频率的波形,因此先根据不同的频率,计算出相应的采样率,编写产生这四个频率正弦波的子程序。在主程序中,判断要调制的码元,决定发送的4个频率的顺序。

信号最终是通过r/o u输出到D/A转换芯片中实现从数字量到模拟量的转换。再经过低通滤波之后,便可得到频率纯净的模拟信号。

3信号的测试、分析。由于4FTSK信号的解调需要调制信号的精度很高,因此设计了测试电路测试发送信号的精确度。测量方法:通过控制输入计数频率值,来测量调制期间的时间长度,发送数据的长度是等于计数频率的周期值X计数值,即计数值除以频率值。

4.2.3 上位机软件实现编码及交织

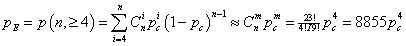

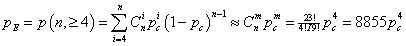

对于本系统而言,在信道中传输中所引起的多次突发错误,对一个码组来说,码组中的差错完全可以看作是独立的。因而在计算输出误码率时,就可以按反映随机信道错误分布的二进制对称信道(BSC)模型计算。在BSC模型中,传输"1"和"0"两种信息,其传输错误的概率相同,均为Pe,传输正确的概率为1-Pe, Pe称为信道误码率。在BSC下,传输长度为n的码组时,正好出现m个差错的概率为

(1)

(1)

码组内出现≧m个差错的概率为

(2)

(2)

在本系统中,交织度为144,所使用差错控制码为Golay (23,12)码,可纠3位错码,因此根据上式,可得误码率为

(3)

(3)

4.2.4 DSP的汇编程序设计

DSP的汇编程序设计包括两部分:系统的ROOT程序设计以及主程序设计。主程序主要是对寄存器的初始化。

4.2.5 PCI接口卡驱动程序设计

在设计和使用PCI设备时,经常要在PC机的软件中访问和控制硬件设备为了保证系统的安全性、稳定性和可移植性,对应用程序访问硬件资源加以限制,这就要求设计设备驱动程序以实现PC机的软件对PCI设备的访问。硬件设备驱动程序的基本功能就是完成设备的初始化、对端口的读写操作以及对内存的直接读写。

5 本文作者创新点

在用单片机实现的基础上,本文提出了以TMS320C5402为主控制器的无线数据调制模块的实现方法,并对其具体实现包括硬件及软件做了比较全面的介绍。可以看出:在速度、精度等很多方面DSP系统都优于单片机系统,而且DSP利用HPI 口和PCI总线,极大的方便了主机与DSP系统的数据交换。该系统灵活、简单,是一种比较先进的技术,具有一定的理论和实践意义。

调制的硬件电路如图3所示。TMS320C5402的IOSTRB和IS相或后作为CA3338的片选信号,通过数据总线将数据送到CA3338中,D/A转换后模拟信号经过运算放大器后输出。

4.2.2 DSP调制程序设计

原始数据在DSP中进行FTSK调制,它是通过DSP的软件编程利用DDS(数字合成频率)的原理实现的。

1 实现方法。DDS(直接数字频率合成)技术是一种把一系列数字量形式的信号通过DAC转换成模拟量形式的信号的合成技术。目前使用最广泛的一种DDS方式是利用高速存储器作查寻表,然后通过高速DAC产生已经用数字形式存入的正弦波。在本系统中,首先,在DSP内部ROM开辟一段存储空间作为一个周期的正弦波抽样点存储器。通过软件对该存储器进行相位一幅值的转换,从而在给定的时间确定相应的输出幅值。发送一个周期的正弦波流程图如图4所示。

2 4FTSK信号的产生及输出。4FTSK信号包含4个频率的波形,因此先根据不同的频率,计算出相应的采样率,编写产生这四个频率正弦波的子程序。在主程序中,判断要调制的码元,决定发送的4个频率的顺序。

信号最终是通过r/o u输出到D/A转换芯片中实现从数字量到模拟量的转换。再经过低通滤波之后,便可得到频率纯净的模拟信号。

3信号的测试、分析。由于4FTSK信号的解调需要调制信号的精度很高,因此设计了测试电路测试发送信号的精确度。测量方法:通过控制输入计数频率值,来测量调制期间的时间长度,发送数据的长度是等于计数频率的周期值X计数值,即计数值除以频率值。

4.2.3 上位机软件实现编码及交织

对于本系统而言,在信道中传输中所引起的多次突发错误,对一个码组来说,码组中的差错完全可以看作是独立的。因而在计算输出误码率时,就可以按反映随机信道错误分布的二进制对称信道(BSC)模型计算。在BSC模型中,传输"1"和"0"两种信息,其传输错误的概率相同,均为Pe,传输正确的概率为1-Pe, Pe称为信道误码率。在BSC下,传输长度为n的码组时,正好出现m个差错的概率为

(1)

(1) 码组内出现≧m个差错的概率为

(2)

(2) 在本系统中,交织度为144,所使用差错控制码为Golay (23,12)码,可纠3位错码,因此根据上式,可得误码率为

(3)

(3) 4.2.4 DSP的汇编程序设计

DSP的汇编程序设计包括两部分:系统的ROOT程序设计以及主程序设计。主程序主要是对寄存器的初始化。

4.2.5 PCI接口卡驱动程序设计

在设计和使用PCI设备时,经常要在PC机的软件中访问和控制硬件设备为了保证系统的安全性、稳定性和可移植性,对应用程序访问硬件资源加以限制,这就要求设计设备驱动程序以实现PC机的软件对PCI设备的访问。硬件设备驱动程序的基本功能就是完成设备的初始化、对端口的读写操作以及对内存的直接读写。

5 本文作者创新点

在用单片机实现的基础上,本文提出了以TMS320C5402为主控制器的无线数据调制模块的实现方法,并对其具体实现包括硬件及软件做了比较全面的介绍。可以看出:在速度、精度等很多方面DSP系统都优于单片机系统,而且DSP利用HPI 口和PCI总线,极大的方便了主机与DSP系统的数据交换。该系统灵活、简单,是一种比较先进的技术,具有一定的理论和实践意义。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)