利用可编程逻辑实现灵活高效的多媒体信号处理

时间:09-14

来源:作者: Tam Do 广播/消费应用业务部高级技术营销经理 Altera公司

点击:

从非常简单的消费类音/视频播放器到在专业制作环境中使用的高度复杂的音视频捕捉、编辑和回放系统,多媒体设备或系统的应用范围非常广泛。人们在实现这类应用系统时会使用特殊应用标准产品(ASSP)、专用数字信号处理器(DSP)、RSIC处理器和可编程逻辑等多种类型的技术。这些技术有各自的独特优势和局限性。

可编程逻辑的好处是灵活性高,易于扩展,可以采用可重配置技术进行多媒体信号处理。由可编程逻辑构成的典型模块有乘法器、存储器、协议接口和时钟电路(如PLL)。这些模块具有可扩展性,能够适应从简单到复杂的各种多媒体处理系统。把繁重的计算工作交给FPGA协处理器,由一个DSP器件和一个FPGA(而不是多达8-10个DSP器件)构成的FPGA高清方案具有更高的性价比。

视频和嵌入式DSP模块

创新的消费类需求,如1080p高清电视、多媒体家庭网关、高带宽效率的机顶盒解码器,一直在推动视频和图像处理应用快速向前发展。低成本FPGA(如Cyclone III系列)的优点是能以ASIC的价格提供DSP性能、高度灵活性和更快的上市速度。Cyclone III系列中成本最低的是EP3C5器件,它拥有的嵌入式乘法器和逻辑资源足以在HDTV 1080p视频应用中完成实时7x7像素滤波功能。面向更高端产品的Stratix III FPGA中所包含的DSP模块可以提供600MHz以上性能的18x18乘法器。Stratix III DSP模块还能以9x9、36x36和新的12x12模式支持可变比特宽度。该DSP模块可以为每个18x18乘法器提供两个9x9或一个半12x12乘法器。如图1所示,级联模式可以把一个DSP模块的输入传送到下一级,进而实现更为卓越的整体性能。Stratix III FPGA的逻辑和存储器结构还针对DSP应用进行了优化,可以用MLAB模块构成抽头延迟线,用ALM(自适应逻辑模块)中的快速3输入加法器构成高效快速的加法器树。

随着图像捕捉、显示器分辩率、高级压缩技术和视频智能方面不断取得重大进展,视频应用所要求的处理带宽也在不断增长。而标准的快速变化和更高的分辨率也促使设计者远离现成技术。用可编程逻辑实现的模块化可编程视频和图像处理方案具有性能高、灵活、升级方便、开发成本低等优点,当产品成熟和生产批量攀升时,可编程逻辑还可提供转移到更低成本的途径。

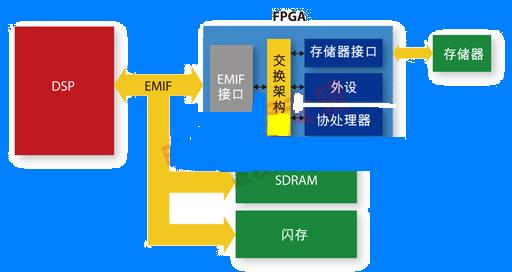

FPGA内部的嵌入式数字信号处理知识产权(IP)可以作为单独的系统方案,也可以与标准的数字信号处理器一起作为协处理器使用。与标准的数字信号处理器相比,FPGA的主要优点是内建有高水平的并行处理机制,如图2所示。而专用的RISC处理器无法满足许多视频和成像应用的所有处理要求。

由于可以把繁重的计算任务交给FPGA协处理器来完成,FPGA方案改善了性价比,见图3。例如,同使用多达8个到10个DSP器件的方案相比,用一个DSP器件和一个FPGA实现的高清方案成本效益更高。ASSP无力支持快速改变和不断发展的视频和成像标准。由于可以方便地通过升级来支持更高的分辨率和最新引入的视频标准,FPGA可以用作视频方案的通用平台。

FPGA的可重新编程能力也消除了设计过时的风险。ASIC需要较长的开发时间,基于ASIC的方案不能像FPGA方案那样方便高效地进行修改。FPGA缩短了上市时间,消除了NRE(非重复工程)成本,可以通过实时改进来支持新兴的标准、新的功能要求或对竞争者发布的新功能做出回应。

一个常见的设计挑战是视频分配通道受到带宽限制。如果利用不同的视频压缩算法限制数字域中的可用带宽,那么在显示经过解码的数据流时将有不同的表现方式。如果提高视频压缩器的压缩比,模块式CODEC的离散余弦变换将产生马赛克噪声或干扰。使用FPGA对视频数据实现预压缩和后压缩可使编码器更容易实现视频压缩,并可进一步改进图像质量,降低传输带宽要求。对于有线、卫星、电信和IPTV广播业务模型来说,由于必须在狭窄的带宽条件下满足高质量要求,这种功能的意义更为重大。

预处理可在视频数据进入编码器之前用2D滤波平滑掉一些高频成分,从而降低马赛克噪声。2D FIR滤波器和中值滤波器功能可以利用3x3、5x5或7x7恒定系数矩阵提供灵活和高效的2D FIR滤波实现方式。

可编程嵌入式处理器

大部分多媒体产品不仅需要进行信号处理,而且需要使用某种类型的微控制器或处理器来完成指令和控制功能或其它日常任务。对于从最小的消费产品到最大的专业视频产品的各类多媒体系统,基于FPGA的嵌入式处理器(如Nios II)向设计者提供了灵活地定制各种要求的能力。多媒体系统开发者面临的一个重大挑战是选择合适的(既不降低性能也不减少功能的)处理器。至今有众多供应商提供了数百种型号的处理器,其外围设备、存储器接口和性能特性也各不相同。

FPGA嵌入式处理器可以降低BOM和PCB版图成本。在需要多个处理器的情况,开发工具将允许用户创建多处理器系统,进而提升系统的性能或把软件应用分成更简单的任务。可以针对最大系统性能或最小逻辑使用率对Nios II内核进行优化,或者在系统性能和逻辑使用率之间取得平衡。该内核可以方便地通过配置实现乘法器、用户设定的高速缓存、定制指令、硬件调试逻辑等特性以适应特殊的性能需求。

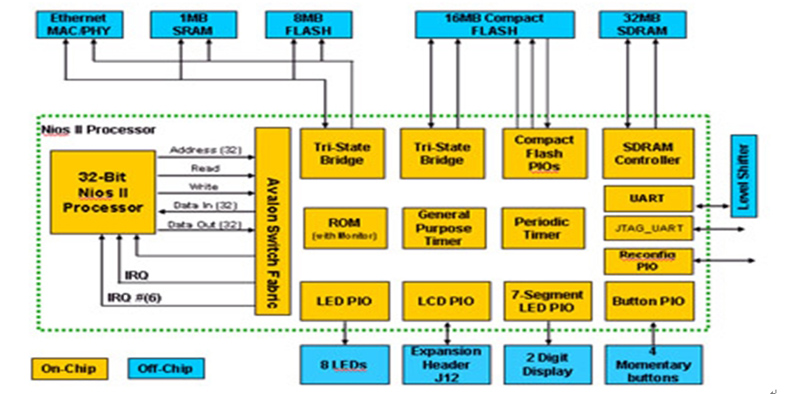

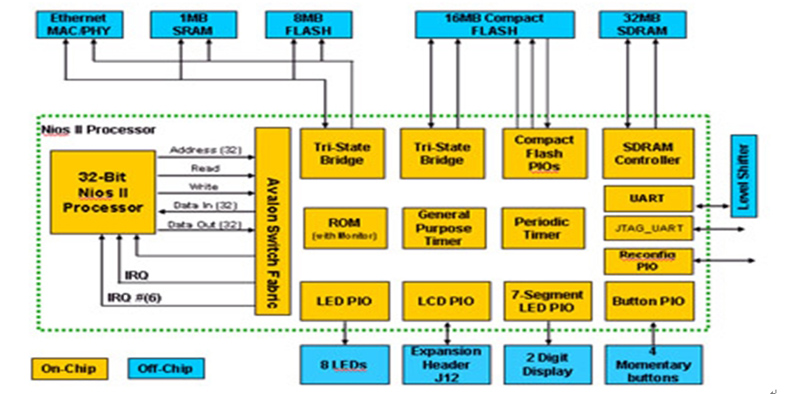

Nios II嵌入式设计套件(EDS)支持创建定制的多内核系统。Nios II处理器与超高密度的FPGA(如Stratix III器件系列产品)相结合可以创建出非常理想的高性能多处理器应用系统。Nios II的典型应用如图4所示。

图4:NIOS II嵌入式处理器的典型系统应用。

可编程逻辑的好处是灵活性高,易于扩展,可以采用可重配置技术进行多媒体信号处理。由可编程逻辑构成的典型模块有乘法器、存储器、协议接口和时钟电路(如PLL)。这些模块具有可扩展性,能够适应从简单到复杂的各种多媒体处理系统。把繁重的计算工作交给FPGA协处理器,由一个DSP器件和一个FPGA(而不是多达8-10个DSP器件)构成的FPGA高清方案具有更高的性价比。

视频和嵌入式DSP模块

创新的消费类需求,如1080p高清电视、多媒体家庭网关、高带宽效率的机顶盒解码器,一直在推动视频和图像处理应用快速向前发展。低成本FPGA(如Cyclone III系列)的优点是能以ASIC的价格提供DSP性能、高度灵活性和更快的上市速度。Cyclone III系列中成本最低的是EP3C5器件,它拥有的嵌入式乘法器和逻辑资源足以在HDTV 1080p视频应用中完成实时7x7像素滤波功能。面向更高端产品的Stratix III FPGA中所包含的DSP模块可以提供600MHz以上性能的18x18乘法器。Stratix III DSP模块还能以9x9、36x36和新的12x12模式支持可变比特宽度。该DSP模块可以为每个18x18乘法器提供两个9x9或一个半12x12乘法器。如图1所示,级联模式可以把一个DSP模块的输入传送到下一级,进而实现更为卓越的整体性能。Stratix III FPGA的逻辑和存储器结构还针对DSP应用进行了优化,可以用MLAB模块构成抽头延迟线,用ALM(自适应逻辑模块)中的快速3输入加法器构成高效快速的加法器树。

随着图像捕捉、显示器分辩率、高级压缩技术和视频智能方面不断取得重大进展,视频应用所要求的处理带宽也在不断增长。而标准的快速变化和更高的分辨率也促使设计者远离现成技术。用可编程逻辑实现的模块化可编程视频和图像处理方案具有性能高、灵活、升级方便、开发成本低等优点,当产品成熟和生产批量攀升时,可编程逻辑还可提供转移到更低成本的途径。

FPGA内部的嵌入式数字信号处理知识产权(IP)可以作为单独的系统方案,也可以与标准的数字信号处理器一起作为协处理器使用。与标准的数字信号处理器相比,FPGA的主要优点是内建有高水平的并行处理机制,如图2所示。而专用的RISC处理器无法满足许多视频和成像应用的所有处理要求。

由于可以把繁重的计算任务交给FPGA协处理器来完成,FPGA方案改善了性价比,见图3。例如,同使用多达8个到10个DSP器件的方案相比,用一个DSP器件和一个FPGA实现的高清方案成本效益更高。ASSP无力支持快速改变和不断发展的视频和成像标准。由于可以方便地通过升级来支持更高的分辨率和最新引入的视频标准,FPGA可以用作视频方案的通用平台。

FPGA的可重新编程能力也消除了设计过时的风险。ASIC需要较长的开发时间,基于ASIC的方案不能像FPGA方案那样方便高效地进行修改。FPGA缩短了上市时间,消除了NRE(非重复工程)成本,可以通过实时改进来支持新兴的标准、新的功能要求或对竞争者发布的新功能做出回应。

一个常见的设计挑战是视频分配通道受到带宽限制。如果利用不同的视频压缩算法限制数字域中的可用带宽,那么在显示经过解码的数据流时将有不同的表现方式。如果提高视频压缩器的压缩比,模块式CODEC的离散余弦变换将产生马赛克噪声或干扰。使用FPGA对视频数据实现预压缩和后压缩可使编码器更容易实现视频压缩,并可进一步改进图像质量,降低传输带宽要求。对于有线、卫星、电信和IPTV广播业务模型来说,由于必须在狭窄的带宽条件下满足高质量要求,这种功能的意义更为重大。

预处理可在视频数据进入编码器之前用2D滤波平滑掉一些高频成分,从而降低马赛克噪声。2D FIR滤波器和中值滤波器功能可以利用3x3、5x5或7x7恒定系数矩阵提供灵活和高效的2D FIR滤波实现方式。

可编程嵌入式处理器

大部分多媒体产品不仅需要进行信号处理,而且需要使用某种类型的微控制器或处理器来完成指令和控制功能或其它日常任务。对于从最小的消费产品到最大的专业视频产品的各类多媒体系统,基于FPGA的嵌入式处理器(如Nios II)向设计者提供了灵活地定制各种要求的能力。多媒体系统开发者面临的一个重大挑战是选择合适的(既不降低性能也不减少功能的)处理器。至今有众多供应商提供了数百种型号的处理器,其外围设备、存储器接口和性能特性也各不相同。

FPGA嵌入式处理器可以降低BOM和PCB版图成本。在需要多个处理器的情况,开发工具将允许用户创建多处理器系统,进而提升系统的性能或把软件应用分成更简单的任务。可以针对最大系统性能或最小逻辑使用率对Nios II内核进行优化,或者在系统性能和逻辑使用率之间取得平衡。该内核可以方便地通过配置实现乘法器、用户设定的高速缓存、定制指令、硬件调试逻辑等特性以适应特殊的性能需求。

Nios II嵌入式设计套件(EDS)支持创建定制的多内核系统。Nios II处理器与超高密度的FPGA(如Stratix III器件系列产品)相结合可以创建出非常理想的高性能多处理器应用系统。Nios II的典型应用如图4所示。

图4:NIOS II嵌入式处理器的典型系统应用。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)