二维DCT编码的DSP实现与优化

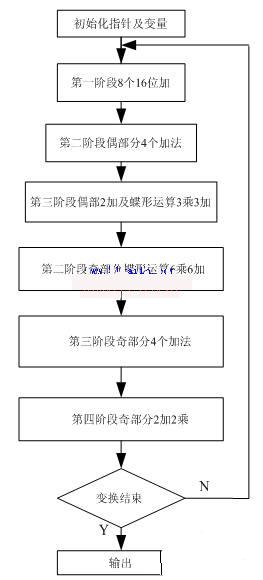

4DSP实现与优化 图2 1维行DCT变换流程图

无论是C语言还是汇编语言,程序流程均分为初始化、行变换、列变换和移位输出四个步骤。行、列变换具有相似性,如果对行变换的结果矩阵转置,则列变换程序跟行变换一样。对于汇编而言,初始化部分主要初始化FP指针以指向前一函数地址,初始化数据和指针寄存器以保存返回数据等。由于DCT行变和列变换过程相似,且列变换是在行变换操作的基础上进行的。则可利用多种索引寻址寄存器的灵活组合,把行变换结果直接以转置方式存储而不增加实际的存储时间,这样行列变换可使用同一代码循环两次实现,减小了实际代码大小。图2一维 DCT变换的流程图。

由于DSP的小数乘法指令是先经过乘法运算后自动调整的,其运算时间比起整数运算要费时。因此,采用先倍乘CONST_SCALE,然后整数运算的方式来节省运算时间。运算的结果需要除以系数CONST_SCALE,这在程序运行时多带来了两次乘法,可以使用左右移位来实现。由于右移位同时会带来移位误差,因此在程序中使用了可选择舍入运算方式。

为了达到更好的精度,在行变换时倍乘后再相加。这可使用Blackfin带有预加/减比例的加法指令在一个指令周期内实现。

程序简化行列变换的代码如下:

B0 = R0;

B3 = R1;

B2 = R2; …

LSETUP (DCT_START, DCT_END) LC0 = P0;

DCT_START:…

LSETUP(ROW_START,ROW_END)LC1=P2;

ROW_START: …

ROW_END:…

B1 = B0;

B0 = B2;

DCT_END:B2 = B1;

程序初始时,R0指向输入矩阵,R2指向中间矩阵,内层循环是行变换过程,该过程结束时,中间矩阵存储着行变换结果的转置。通过B0和B2的指针交换,把中间矩阵当作输入进行行变换,这样,把原输入矩阵变成了输出矩阵,并且矩阵中各元素位置不变。

比较式(1)和(3)发现,二维DCT 变换时结果为两次无理数sqrt(8)相乘,产生了有理项,因此,在程序里首先多乘一次sqrt(8),然后在两次DCT 变换结束以后,使用右移3位以达到正常输出。

为了评估优化后的效果,在ADSP-BF533 EZLITE平台和VisualDSP4.5环境下,当BF533

工作在核心频率594MHZ时,对一源图像点阵灰度数据进行DCT处理。该灰度图像为一个8×8的数组A[6],对A进行二维 DCT 调用,实际运行结果为:C语言代码为392 bytes,执行时间为3.806397 μs;汇编语言代码为248 bytes,执行时间为1.085859μs。显然,与以C语言为主的二维DCT编码相比,用汇编语言实现的二维DCT编码在代码大小、代码执行时间上均得到了很大改善。

5 结论

本文创新之处在于能根据ADSP-BF533的结构和指令特点及视频信号压缩的实时性要求,使用汇编语言对视频信号进行了二维DCT编码及优化。实验证明:在ADSP-BF533硬件平台和VisualDSP4.5环境下,当 CPU运行在594MHZ时,使用汇编语言实现的DCT变换比C语言实现的DCT变换执行时间减小71.4%,代码空间减小近30%。以标准CIF 测试序列为例,压缩一张352×288的图片能减少4.31ms,可见优化效果显着。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)