基于Visual DSP++4.0开发的TigerSHARC DSP多处理器系统及其应用

时间:06-14

来源:作者:杨荣华,张弓

点击:

3 ID检测

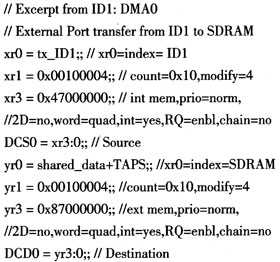

在多处理器系统构建完成后,接下来还要注意:所生成的可执行文件要载人到该系统中正确的DSP中,以免出错,以下子程序可用于检测所生成的可执行文件是否载入到了系统中正确的DSP中,以确保没有ID失配:

4结束语

除了多处理器系统的构建方法和数据传输的模式外,MP系统应用中还有DSP资源的分配、总线连接和多DSP系统与FPGA等内容。随着ADSP-TS201S芯片的广泛应用,该处理器的运算速度、存储能力和通信逻辑处理优势已明显的表现出来,而且链路口的传输速度、可靠性和灵活性也较以前有了较大的改观。TigerSHARC功能强大的运算单元和支持多处理器并行处理的特性,使得它特别适用于复杂的系统,如国防工业、医用图像处理以及复杂无线通信算法的处理。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)