利用优化的DSP加快无线基础设施的设计

时间:06-03

来源:

点击:

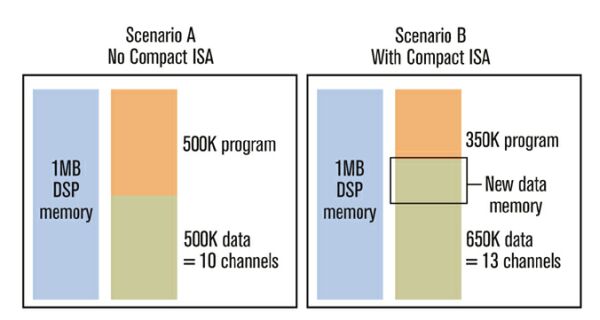

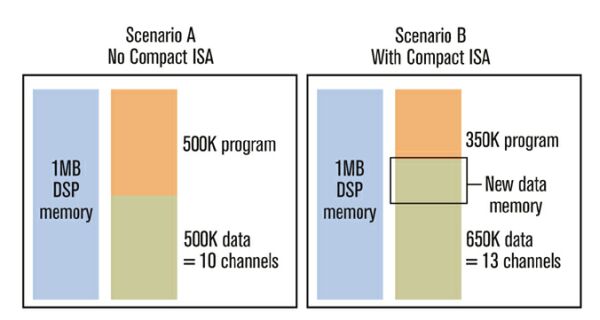

快速的软件方式

专门针对CI应用的DSP的软件环境和架构对系统的吞吐性能、总开发成本和上市时间也有着极大的影响。新的或者增强的指令一般被集成到CI DSP中,以获得特定于无线通信的某些重复功能。例如,新的指令集架构(ISA)可以通过加快其符号率、芯片速率和矩阵算术处理来提高基站中的DSP性能。先进的ISA还可以通过实现密度更高的电路板来降低系统的每通道成本。有效的ISA可以降低系统软件代码的大小,从而减少专用于外部存储器的板空间,或者为关键任务数据释放存储容量(如图3所示)。通用DSP的确可以通过编程来执行通信功能,但是如果没有特定于CI的ISA,与具有CI ISA的经过优化的DSP相比,在一般DSP上运行的相同功能将需要3~4倍的指令、更多的代码空间和更长的编程时间。

除了针对CI应用的ISA之外,一些供应商还提供专门针对DSP优化的CI功能例程库。通过一个命令,这些例程可以执行以前需要单独执行的多个功能,同时又减少了代码大小并且提高了性能。

一代CI DSP与下一代CI DSP之间的软件连贯性也对开发周期和新CI系统的上市时间有极大影响。为了维持合理的开发成本,一个DSP的多数软件必须进行迁移并在下一代器件中重复使用。

针对CI进行优化

由于CI市场的各种错综特征、复杂性和特别要求,大多数通用DSP都不再是无线基站等应用中针对CI优化的DSP。在要求较高的设施系统中部署现成的DSP将需要制造商额外的设计工作,从而导致系统上市时间的延长。但是同样重要的是,它们还可以通过适当的加速器、高速内部内存、通信协处理器、复杂的CI特定软件和许多其它功能提供一组完整的外围接口和内存接口,从而精简系统开发过程并加快高吞吐能力系统的交付。

专门针对CI应用的DSP的软件环境和架构对系统的吞吐性能、总开发成本和上市时间也有着极大的影响。新的或者增强的指令一般被集成到CI DSP中,以获得特定于无线通信的某些重复功能。例如,新的指令集架构(ISA)可以通过加快其符号率、芯片速率和矩阵算术处理来提高基站中的DSP性能。先进的ISA还可以通过实现密度更高的电路板来降低系统的每通道成本。有效的ISA可以降低系统软件代码的大小,从而减少专用于外部存储器的板空间,或者为关键任务数据释放存储容量(如图3所示)。通用DSP的确可以通过编程来执行通信功能,但是如果没有特定于CI的ISA,与具有CI ISA的经过优化的DSP相比,在一般DSP上运行的相同功能将需要3~4倍的指令、更多的代码空间和更长的编程时间。

除了针对CI应用的ISA之外,一些供应商还提供专门针对DSP优化的CI功能例程库。通过一个命令,这些例程可以执行以前需要单独执行的多个功能,同时又减少了代码大小并且提高了性能。

一代CI DSP与下一代CI DSP之间的软件连贯性也对开发周期和新CI系统的上市时间有极大影响。为了维持合理的开发成本,一个DSP的多数软件必须进行迁移并在下一代器件中重复使用。

针对CI进行优化

由于CI市场的各种错综特征、复杂性和特别要求,大多数通用DSP都不再是无线基站等应用中针对CI优化的DSP。在要求较高的设施系统中部署现成的DSP将需要制造商额外的设计工作,从而导致系统上市时间的延长。但是同样重要的是,它们还可以通过适当的加速器、高速内部内存、通信协处理器、复杂的CI特定软件和许多其它功能提供一组完整的外围接口和内存接口,从而精简系统开发过程并加快高吞吐能力系统的交付。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)