基于DSP的磁流变阻尼器的控制方法

摘要: 以美国德州仪器公司推出的十六位定点通用数字信号处理芯片DSP为核心开发出精确可控的电流控制器,电流可在0~1.5A范围内调节,输出电流精度高,线性度好,控制效果显著。

关键词:DSP; 电流控制器; 磁流变阻尼器; PWM控制

中图分类号:TP2 文献标识码:B 文章编号:

1 引言

磁流变阻尼器是一种在磁场作用下阻尼可控的器件,在航空、汽车等领域具有广泛应用前景。与传统汽车悬架系统相比,装有磁流变阻尼器的半主动悬架系统可以根据路面状况和车辆运行状态在计算机的控制下自动调节阻尼器的阻尼力,大大提高汽车的舒适性和行车安全性[1,2]。磁流变阻尼器的工作原理是改变励磁线圈中的电流从而获得不同强度的磁场,使工作腔中的磁流变液的流动特性发生变化,从而改变阻尼力的大小。因此,控制器只要能实时精确调节磁流变阻尼器的驱动电流,就能达到控制磁流变阻尼器的目的。经文献检索,国内外未见磁流变阻尼器的电流控制器设计的报道。根据美国LOAD公司的网站最新发布的信息,LOAD公司已经研制出了适用于LOAD公司生产的Rheonetic系列磁流变器件的电流控制器RD-3002。它可以工作在手动调节和外加电压控制调节两种方式下,能与计算机或PLC构成闭环控制系统。RD-3002需要外加12V,2A的电源,外加控制电压:0~5V,输出电流:0~2A。但是他们没有公布设计的原理和实现的方法。

美国德州仪器公司(Texas Instrument)推出的定点十六位通用数字信号处理芯片TMS320F240,采用改进哈佛结构,程序存储器和数据存储器的总线分开,可以最大限度提高处理能力。为了适合工业控制要求,F240集成了许多外设,包括3个16位通用定时器,12路带死区控制的PWM输出、双通道10位A/D输入,串行通信接口以及Watchdog、PLL电路。因此,我们充分利用F240的硬件资源,根据PWM信号控制开关器件调节电流的原理,顺利地设计出磁流变阻尼器的的控制器,并且F240的强大处理能力为今后系统扩展留有余地。下面将详细介绍基于DSP的磁流变阻尼器的控制器的设计原理和控制方法。

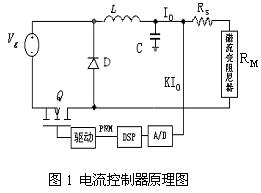

RS为采样电阻,KI0表示输出电流的采样,K为增益系数, KI0输入到DSP集成的A/D口,DSP 对采样信号进行运算后,根据相应控制策略输出一定占空比的PWM信号,控制主回路的输出电流大小。

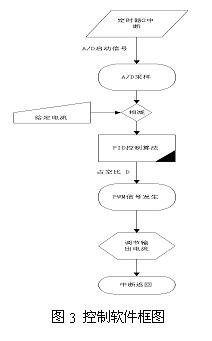

控制器的软件采用F240汇编语言设计,框图如图3所示。系统工作时主程序可以处理其它事务,当定时器2发生周期中断时,触发A/D采样,然后采样值与系统给定值相减,误差输入PID控制模块,输出PWM信号的占空比D,D送给PWM信号发生模块,产生的PWM信号用于控制驱动电流的输出。

3 A/D采样

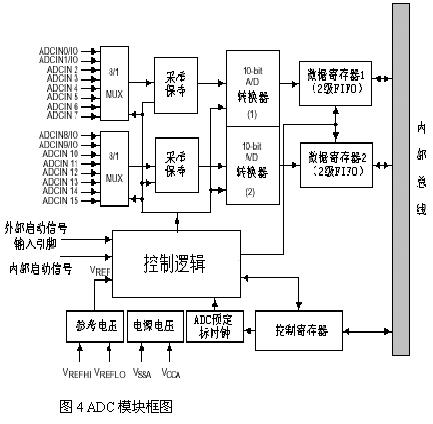

F240内部集成了两个带采样-保持电路的10位ADC模块。每个模块有8个模拟输入通道,它们通过一个8选1模拟多路转换器提供给ADC。每个ADC单元的最大转换事件为6.6μs[3]。ADC模块的参考电压必须由外部电源提供,上级参考电压和下级参考电压可以设置为小于或等于5Vdc的任意值,分别接到VREFHI和VREFLO引脚。VCCA和VSSA引脚必须分别接到5Vdc和模拟地。ADC模块框图如图4所示。

本系统采用ADC1模块的1通道输入采样信号,采用定时器2周期中断触发方式,操作步骤如下:

1) 设置定时器控制器GPTCON的位9,10为0,1,将定时器2的周期中断作为ADC的内部启动信号。

2) 设置ADC控制寄存器1(ADCCTRL1)。

位12 清0,禁止ADC2(没有用到ADC2);

位11置1, ADC1被使能;

位10清0, 非连续转换模式;

位9 置1,当AD转换完成后产生一个中断;

位8 置1,ADC中断标志位,当AD转换完成后该位被置1;

位6-4 ADC2通道选择;

位3-1置为 000 ,ADC1通道选择,000为通道1;

位0 置1, AD开始转换;

3) 设置ADC控制寄存器2(ADCTRL2)。

位10 置1,ADC转换与一个事件管理器信号同步(GPT2的周期中断信号);

位9 清0,屏蔽外部信号触发;

位2-0置为 101, 输入时钟预定标为16。单个ADC模块在一个ADC预定标时钟周期内完成输入的采样,在5个 ADC预定标时钟周期内完成转换,所以一次采样/转换需要6个预定标时钟周期内完成。ADC模块的结构要求采样/转换时间要等于或大于6μs才能保证转换正确。预定标值必须满足:SYSCLK时钟周期×预定标值×6≥6μs。

在系统中设置SYSCLK时钟周期为0.1μs,0.1μs×16×6=9.6μs≥6μs。

4) 读ADC1的数字结果寄存器。

ADC的数字结果寄存器是一个2深度的FIFO的只读寄存器,位15-6是实际的10位转换值。位5-0保留。

4 PWM波形的生成

F240具有12个器件引脚用于PWM信号输出,具有以下特点:

•16位的最大PWM分辨率;

•PWM载波频率可以实时改变(双缓冲的周期寄存器);

•PWM脉宽可以实时改变(双缓冲的比较寄存器);

•功率驱动保护中断,可以监控程序提供的驱动异常,如过电压、过电流和温升过高;

•可以编程产生对称、非对称和空间向量的PWM波形;

•比较和周期寄存器自动重载,使CPU开销最小;

•全比较单元的三对引脚还可以输出带死区的PWM波形,死区宽度在0~2048个CPU时钟周期内可编程。

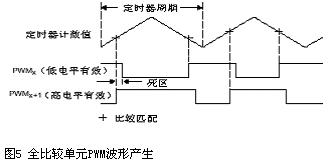

要产生一个PWM信号,需要一个合适的定时器来重复产生一个与PWM周期相同的计数周期,一个比较寄存器保持调制值。比较寄存器的值不断与定时器的计数值相比较,当两个值匹配时,在相应的输出上就会产生一个转换(从低到高或从高到低)。当两个值之间的第二次匹配产生或一个定时器周期结束时,相应的输出上又会产生一次转换(从高到低或从低到高)。通过这种方法所产生的输出脉冲的开关时间就会与比较寄存器的值成比例。在每定时器周期中,这个过程都会出现,通过改变比较寄存器的值,就能产生一个PWM信号,见图5。

本系统用全比较单元PWM1/CMP1引脚产生100kHz的对称PWM波形,具体步骤如下。

1) 设置和载入全比较动作控制寄存器ACTR:SPLK #0000011001100101b, ACTR

位1-0 置为10使PWM1 高电平有效,在比较寄存器的值与定时器的计数值相匹配时,PWM1输出产生一个从低到高转换,第二次匹配又产生从高到低的转换。

2) 初始化全比较单元1比较寄存器CMPR1:SPLK #0000h, CMPR1。

3) 设置和载入比较控制寄存器:SPLK #0100101111010111B, COMCON 。

位15清0,禁止全比较操作;

位14-13,置为10 立即重载比较寄存器CMPR1的值;

位12清0,禁止空间向量输出;

位11-10,置为10立即重载动作控制寄存器ACTR的值;

位9置1,PWM输出使能;

位0置1,PWM1/CMP1引脚输出模式为PWM模式。

4)设置和载入比较控制寄存器:SPLK #1100101111010111B, COMCON。

位15置1,全比较操作使能。

5)设置和载入定时器 GP1的周期寄存器T1PR:SPLK #100, T1PR。

连续加/减计数模式下,当CPU时钟频率=20MHz时,PWM的载波频率= 20MHz/(100*2)。

6)设置和载入比较寄存器CMPR1,确定PWM波形的脉宽:SPLK #50, CMPR1。

PWM波形的占空比=50/100*100%=50%。

7)设置和载入GP1的计数寄存器T1CNT:SPLK #0FFFEH,T1CNT。

初始化GP1的计数寄存器值。

8)设置和载入定时器 GP1的控制寄存器T1CON,启动操作:

SPLK #1010100001000000b, T1CON;

位13-11置为101, GP1处于连续加/减计数模式;

位10-8置为000,输入时钟预定标GP1时钟周期=CPU时钟周期;

位6 置1允许GP1操作;

位5-4置为00,时钟源使用内部时钟;

位3-2置为00,GP1计数器值为0时重载;

位1清0,禁止GP1比较操作。

注意:

1) 使用全比较单元产生PWM波形,只能使用定时器GP1;

2) 为确保所有全比较输出的起始状态正确,COMCON必须被写入两次。

5 测试结果

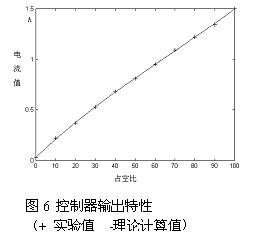

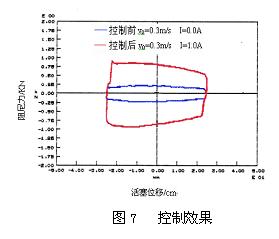

电流控制器输出特性见图6,从图中可以看出实验结果与理论计算相吻合,输出电流与PWM信号占空比成线形关系。电流控制器对磁流变阻尼器的控制效果见图7,从图中可以看出,随着线圈电流强度的增加,示功图的面积逐渐增大,表明了减振器的阻尼力增大和在一个循环中减振器所耗散的功增大,控制效果非常明显。

6 结论

本文以美国德州仪器公司的定点十六位通用数字信号处理芯片TMS320F240为核心设计了用于磁流变阻尼器的电流控制器,经实验证明

(1) F240具有丰富的外设资源,极高的性价比,尤其是它集成了12路PWM输出和16路10位A/D转换,采用它可以提高系统的集成度和可靠性,缩短研发周期,为自动控制系统开发人员提供了一种新的选择;

(2) 基于F240的电流控制器可在0~1.5A范围内连续调节,响应速度快,输出线性度较好,输出稳定性好(输出电流变化<0.03A),控制效果显著。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)