DSP+FPGA嵌入式多路视频监控系统硬件平台

4通道视频解码器TVP5154概述

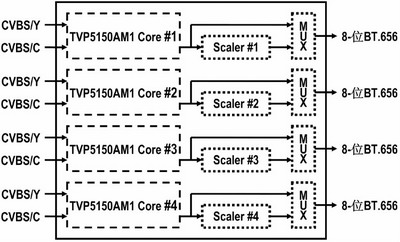

本文介绍的DSP + FPGA嵌入式多通道视频监控系统硬件平台有8个模拟视频输入通道,选用TI的单片4通道视频解码器TVP5154,其原理框图如图2。

图2 4通道视频解码器TVP5154原理框图

TVP5454的特点是内含4个独立的TVP5150单通道视频解码器、4个独立的缩放器和1个IIC总线,将4通道标准模拟视频输入转换成4 通道8位数字视频输出。每个通道可接受1路超级视频输入或2路复合视频输入;每个通道的缩放器水平、垂直方向均可独立缩放1/4x~4x;每个通道的数字视频输出接口既可是8位YCbCr 4:2:2的BT.656(内嵌行、场同步码),也可是8位YCbCr 4:2:2的带行、场同步信号的数字视频流;可通过IIC总线分别或广播配置和获取4个视频解码器或4个缩放器的控制和状态信息。

Xilinx Spartan-3系列FPGA概述

8通道模拟视频输入需要2片TVP5154视频解码器,总有8个8位BT.656数字视频接口,而DM6437视频前端VPFE只有1个视频输入口,为了实现8通道视频输入,二者之间需要耦合逻辑,此耦合逻辑的基本功能需要实现:

*接收/缓冲8个8位BT.656数字视频输入数据(像素时钟为27MHz)

*每个通道水平/垂直均缩小1/2,由D1格式缩小为CIF格式

*将8个CIF格式的数字视频拼接成1个8-位、54MHz、YCbCr 4:2:2带行、场同步的数字视频流,以接口DM6437的视频前端VPFE

除了这些基本功能外,还可以利用FPGA丰富的资源和强大的性能,实现很多视频预处理的功能,如滤波、防眩光等,甚至实现目标侦测、跟踪等目标视频热门功能。

Xilinx Spartan-3系列FPGA的结构框图如图3所示。

图3 Spartan-3系列FPGA结构

其中的功能单元如下:

红色方块代表可配置逻辑块CLBs,其由查找表LUT和触发器造成,是实现组合和时序电路的主要逻辑资源,查找表LUT用于实现组合逻辑或16×1存储器或16位移位寄存器,触发器用于实现时序逻辑。

蓝色方块代表数字时钟管理器DCM,实现时钟信号的倍频/分频、相移、时滞等控制。

绿色方块代表块存储器BRAM,每个块存储器为18K-位双口RAM块,用于作数据缓存。

黄色方块代表乘法器或乘累加器DSP48A,用于实现数字信号运算。

褐色方块代表输入/输出块IOBs,精选多种常用的I/O标准,方便与各种外部信号直接接口。

DPS + FPGA嵌入式多路视频监控系统设计要点

DSP + FPGA嵌入式多路视频监控系统硬件平台的设计要点在于视频接口的实现。

视频接口涉及标准模拟视频的输入/输出,输入的模拟视频需要数字化(解码器),输出的数字视频信号需要转换为模拟视频信号(编码器)以驱动显示器,以及视频编码器/解码器如何与TMS320DM6437进行接口。

在设计视频接口之前,首先,来看一下视频接口的总体设计要求:

*模拟视频输入: 8路标准的PAL/NTSC模拟视频输入,复合视频CVBS、超级视频Y/C

*模拟视频输出: 1路标准PAL/NTSC模拟视频输出,复合视频CVBS、超级视频Y/C、或分量视频YPbPr或RGB,以方便本地预览或测试

其次,选择视频解码器和编码器,以及它们的接口特点:

*视频解码器: 2片TVP5154,接受8路标准模拟视频输入,8路8位BT.656数字视频数据流输出

•输入口:标准模拟视频输入,复合视频CVBS、或超级视频Y/C

•数据口:8位数据线,时钟SCLK,行/场同步控制信号HSYNC、VSYNC、FID等

•控制口:IIC总线,用于设置视频解码器工作参数和反馈状态信息

*视频编码器: 直接由TMS320DM6437片上视频处理后端实现1路标准模拟视频输出CVBS、或S-Video、或分量视频

再次,需要具体来了解TMS320DM6437视频处理子系统的特点:

*视频处理前端VPFE

•16-位数据:CI[7:0]/CCD[15:8]、YI[7:0]/CCD[7:0]

•同步信号:像素时钟、行同步、帧同步、场标志

*视频处理后端VPBE

•模拟视频接口:复合视频CVBS、或超级视频Y/C、或分量视频YPbPr/RGB

•数字视频接口:24-位数据、行/场同步信号等

最后,为了实现2个视频解码器,总8通道数字视频数据流与TMS320DM6437视频前端接口,在视频解码器与TMS320DM6437之间需要用FPGA来实现耦合逻辑,FPGA需实现的功能如下:

*接收/缓冲来自视频解码器的8路8位BT.656数字视频数据流(像素时钟为27MHz)

*每个通道水平/垂直均缩小1/2,将D1格式图像缩小为CIF格式图像

*将8路CIF格式的数字视频数据拼接成1路8位、54MHz、D1格式的数字视频数据流,以接口DM6437视频处理前端VPFE

*可通过软件设置, 在8路视频输入中任选1路D1格式的视频数据,接口DM6437 的8位EMIFA总线,用于实现预览

TMS320DM6437视频处理子系统的具体配置如下:

*DM6437视频前端VPFE配置为8位、54MHz数字视频口,实现8路CIF格式视频输入

*DM6437视频后端VPBE配置为模拟视频输出,直接驱动监视器

DSP + FPGA嵌入式多路视频处理系统硬件平台的视频口如图4所示。

图4 系统硬件平台的视频口

FPGA DSP Xilinx 数字视频 Davinci系列 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)