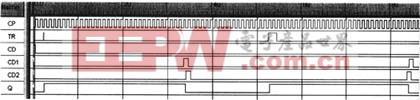

基于CPLD器件设计的单稳态电路

时间:08-10

来源:互联网

点击:

- 基于CPLD器件的单稳态脉冲展宽电路(06-05)

- DSP外围电路(10-09)

- TMS32OF2812与DIP-IPM的通用电路设计(07-31)

- TMS320F206外围电路典型设计 (04-17)

- 基于DSP芯片TMS320LF2407A的超声电源系统的控制电路(08-01)

- 多片DDC芯片HSP50214B与DSP接口电路设计(08-21)