基于CPLD器件设计的单稳态电路

1 基于CPLD器件的单稳态脉冲展宽电路

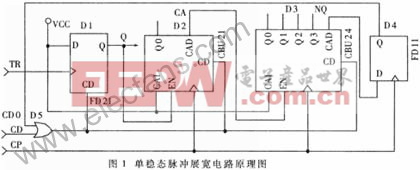

在众多的CPLD器件中,LatTIce公司在GAL基础上利用isp技术开发出了一系列ispLSI在线可编程逻辑器件(以下简称isp器件),其原理和特点在许多杂志上早有报道,而且国内已有相当多的电路设计人员非常熟悉。Lattice公司的isp器件给笔者印象最深的是其工作的可靠性比较高。图1即是一种将输入的窄脉冲信号展宽成具有一定宽度和精度的宽脉冲信号的电路原理图。

图中,TR为输入的窄脉冲雷达信号;CP为输入的系统时钟脉冲信号;Q即是单稳态脉冲展宽电路输出的宽脉冲信号。图中的单元电路符号D1既是展宽脉冲的前沿产生电路,又是展宽脉冲宽度形成电路;D2、D3是二进制计数器,主要用作展宽脉冲的宽度控制电路。根据对脉冲宽度的不同要求,可以采用不同位数的二进制或其它进制的计数器 (这里,脉冲宽度的设计值是3.2μs,而CP脉冲的周期值是0.1μs);D4是展宽脉冲后沿产生电路,当计数器D3的进位输出端NQ为"高",且CP脉冲的上升沿到达时,D4输出端输出一正向脉冲信号,经D5送至D1的CD清零端,从而结束了一个窄脉冲信号的展宽过程,从D1的Q输出端输出一完整的展宽脉冲信号。同时,D5的输出信号还送至D2、D3的CD清零端,将其清零后,等待下一个窄脉冲的到来。从图1所示的电路原理图中可以看到,通常可以将D3的进位输出信号NQ直接送入D5输入端,作为D1、D2、D3的清零 脉冲信号。

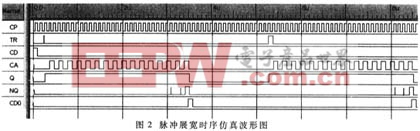

但从图2所示的时序仿真波形中可以看到,D3的进位输出NQ波形中,除有正常的进位脉冲信号输出外,在其前面还有宽度和数量不等的干扰窄脉冲。如果将NQ脉冲经D5后直接作为D1的清零信号,则展宽脉冲的宽度将受干扰窄脉冲的影响而不稳定,因为isp器件中触发器的清零操作过程是异步进行的。采用D4后,只有与计数时钟脉冲具有同步关系的那个进位脉冲,才能在D4的输出端形成清零脉冲。这样就完全排除了那些干扰窄脉冲的影响,从而保证了展宽脉冲宽度的稳定性和准确性。图2是这种脉冲展宽的时序仿真波形图。所用的器件是Lattice公司的ispLSI1032/883-64PIN的PGA封装器件。

2 基于CPLD器件脉冲展宽电路的特点

从上面的电路原理图和时序仿真波形图可以看出,利用isp器件构成的脉冲展宽电路具有如下特点:

(1)对输入脉冲信号的宽度适应能力较强。最窄可以到ns量级,因其仅与所采用的CPLD器件的工作速度有关。因此,特别适用于对窄脉冲雷达信号进行展宽。

(2)展宽脉冲的宽度可以根据需要任意设定,亦可改变电路(例如与单片机相结合)使其做到现场实时自动加载。

(3)展宽脉冲的宽度稳定、准确。因无外接R、C定时元器件,其脉冲宽度仅与所采用的时钟频率和CPLD器件的性能有关。

(4)展宽脉冲的前沿与输入窄脉冲的前沿之间的延迟时间基本恒定,即这个延迟时间是信号从D1的时钟输入端到D1的输出端Q的延迟时间。

(5)电路调试简单。当需要调整展宽脉冲的宽度时,不需更换元器件,只要将重新设计、仿真通过后的JED熔丝图文件,通过加载电缆适时加载到CPLD器件内即可。这在对电路进行高、低温等例行试验时变得极为简单、方便和高效。

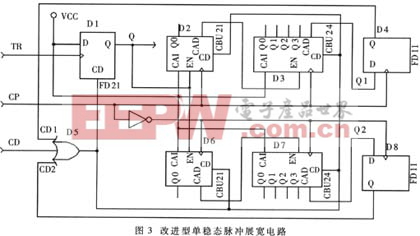

从图1还可以看出,这种单稳态脉冲展宽电路产生的脉宽精度是小于+或-一个CP时钟周期。若要提高展宽脉冲宽度的精度,可以采用图3所示的改进型单稳态脉冲展宽电路,即在图1电路的基础上,将进入isp器件的时钟脉冲信号经反相器反相后,作为另一个相同脉宽控制电路的计数器的时钟脉冲。

这样,如果输入的窄脉冲在时钟脉冲的前半周期内到达,则由D6、D7、D8组成的脉宽控制电路先开始计数;如果输入的窄脉冲在时钟脉冲的后半周期内到达,则由D2、D3、D4组成的脉宽控制电路先开始计数。由于上下两个脉宽控制电路的时间计数值是相同的,故先计数则先结束,后计数则后结束。两者之差为半个时钟周期值。展宽脉冲信号的宽度,始于输入窄脉冲的前沿,而止于两个脉宽控制电路中最早结束定时计数的那个计数器的进位脉冲所产生的清零脉冲信号。因此,不管输入窄脉冲信号的前沿与时钟脉冲的相对时间关系如何,其输出展宽脉冲的宽度为脉宽控制电路的时间计数值与输入窄脉冲的前沿加上时钟脉冲的前沿或后沿之差。尽管脉宽控制计数电路的时钟脉冲周期没有改变,但由于输入窄脉冲的前沿与控制计数电路时钟脉冲上升沿的最大时差只有半个时钟脉冲周期(注意:时钟脉冲信号的占空比为1:1),故展宽脉冲信号的宽度误差小于"+"或-半个时钟脉冲周期。图4是图3所示电路的时序仿真波形图。

这样,如果输入的窄脉冲在时钟脉冲的前半周期内到达,则由D6、D7、D8组成的脉宽控制电路先开始计数;如果输入的窄脉冲在时钟脉冲的后半周期内到达,则由D2、D3、D4组成的脉宽控制电路先开始计数。由于上下两个脉宽控制电路的时间计数值是相同的,故先计数则先结束,后计数则后结束。两者之差为半个时钟周期值。展宽脉冲信号的宽度,始于输入窄脉冲的前沿,而止于两个脉宽控制电路中最早结束定时计数的那个计数器的进位脉冲所产生的清零脉冲信号。因此,不管输入窄脉冲信号的前沿与时钟脉冲的相对时间关系如何,其输出展宽脉冲的宽度为脉宽控制电路的时间计数值与输入窄脉冲的前沿加上时钟脉冲的前沿或后沿之差。尽管脉宽控制计数电路的时钟脉冲周期没有改变,但由于输入窄脉冲的前沿与控制计数电路时钟脉冲上升沿的最大时差只有半个时钟脉冲周期(注意:时钟脉冲信号的占空比为1:1),故展宽脉冲信号的宽度误差小于"+"或-半个时钟脉冲周期。图4是图3所示电路的时序仿真波形图。

- 基于CPLD器件的单稳态脉冲展宽电路(06-05)

- DSP外围电路(10-09)

- TMS32OF2812与DIP-IPM的通用电路设计(07-31)

- TMS320F206外围电路典型设计 (04-17)

- 基于DSP芯片TMS320LF2407A的超声电源系统的控制电路(08-01)

- 多片DDC芯片HSP50214B与DSP接口电路设计(08-21)