基于MAX7000系列CPLD的数据采集系统

时间:10-22

来源:互联网

点击:

号经解码电路输出一个锁存脉冲到锁存器(L),将此低8位地址锁存;然后通过391H端口将高4位地址送到数据总线上,此时由PC-AB送出的391H信号和IOW信号经解码电路输出一个锁存脉冲到锁存器(H),将此高4位地址锁存;最后通过392H端口进行读写,只要PC-AB上出现392H信号,解码电路就输出一个低电平到双口RAM的/CS,再根据相应的读写控制信号就能进行读写操作。

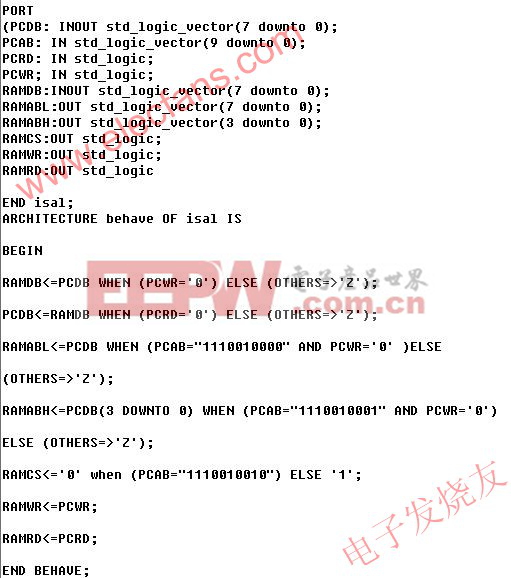

用ALTERA公司的EPM7064SLC84-5实现这一接口的VHDL文件如下:

仿真结果表明此电路设计完全可以实现上述功能。PC机使用端口392H读取双口RAM中的数据时的仿真图如图4所示。

数据采集 系统 CPLD 系列 MAX7000 基于 相关文章:

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 基于DSP和USB的三维感应测井数据采集系统(06-14)

- 多通道同步数据采集及压缩系统(08-12)

- 基于DSP的高速数据采集系统设计方案(06-25)