一种基于FPGA的信道化接收机的研究与设计

时间:11-28

来源:互联网

点击:

IR滤波器,减小FPGA用于存储系数的RAM资源;2)DFT可以用快速傅里叶变换FFT实现,提高计算效率;3)由于采用多相滤波结构,计算量上极大地减少,可实现性增强。这些优点为信道化结构的工程实现提供很好途径。

4 测试结果

系统输入测试信号为单频正弦信号,VPP为1 V,信号经过AD采样,DDC,信道化后,数据结果经过PCI上传给PC机作分析和显示。

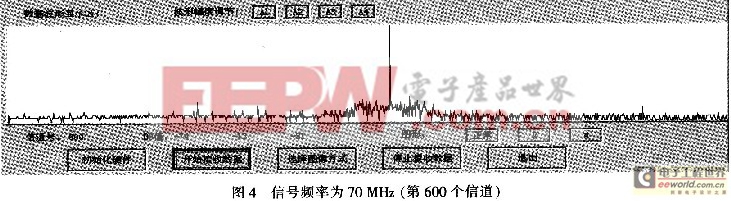

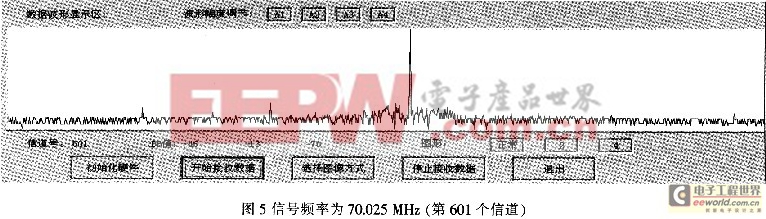

用Microsoft Visual C++6.0制作的界面中:横坐标是信道号,纵坐标是归一化功率值(dB),以数据形式显示的内容有:信号功率最大值对应的信道号、子信道输出相对于输入幅度的dB值以及相邻的两个信道的dB值。如图4和图5所示,输入信号频率分别为70 MHz,70.025 MHz,经过信道化后,在对应的信道号上都能输出谱线,频率分辨率达到25 kHz。经过多次重复测试,系统对相邻信道的带外抑制都达到55 dB以上。

5 结论

该系统主要器件包括AD6645、EP2S60,其中AD6654实现ADC,EP2S60负责系统控制、通信、算法实现,最终来实现了信道化接收功能。因此,该系统具有高度的灵活性和很强的通用性,可通过软件的重载或升级完成不同指标要求、不同模式的系统结构。在多板连接时,可以构成一个更大的阵列系统,可以用于DOA和DBF。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)