基于FPGA的灰度形态学滤波器实现

摘 要: 阐述了灰度形态学滤波的原理和基本操作,给出了3×3结构元素灰度形态学滤波器的硬件结构,详细描述了该滤波器在Xilinx公司的XC2S400E芯片上实现的过程和仿真的方法,并说明了需要注意的问题。

数学形态学滤波是数字图像处理和计算机视觉研究中的一种新方法,已广泛应用于计算机视觉、图像处理、视觉检测、纹理和场景分析等方面。上述这些应用都有时间限制,要求实时处理。数学形态学滤波作为一种非线性滤波技术,其理论基础是集合论,具有天然的并行结构,便于硬件电路实现[1]。但形态学滤波的硬件实现是以牺牲硬件资源为代价的。对于一幅较大的灰度图像,如果采用常规器件实现,硬件结构会相当庞大。

随着微电子技术的发展,现场可编程门阵列(Field Program Gates Array,FPGA)器件已经朝着高密度、低压、低功耗的方向发展。由于FPGA芯片门数不断增加,PLL/DLL、Distributed RAM、Block RAM等片内资源以及设计所需的IP库越来越丰富,所有这些使得基于FPGA的数学形态学滤波器实现成为可能。本文综合考虑了数学形态学滤波器的并行特性和FPGA器件的特点,在Xilinx公司的XC2S400E芯片上实现了灰度图像的开操作形态学滤波器。

1 灰度形态学滤波基本知识[2]

数学形态学是一种数字图像处理的新方法,其研究的主要目的在于描述图像的基本结构和特征,主要内容是在积分几何和随机集合论的基础上,设计一整套变换、概念和算法,以描述图像的各个象素之间的关系。它的基本思想是用具有一定形态的结构元去度量和提取图像中的对应形态以达到对图像分析和识别的目的。形态学的应用可以简化图像数据,保持它们基本的形状特性,并除去不相干的结构。

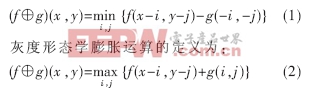

形态学的基本运算有4种:膨胀、腐蚀、开和闭。灰度图像的腐蚀和膨胀过程可直接从图像及结构元素的灰度级函数计算出来。对图像中的某一点f(x,y),灰度形态学腐蚀运算的定义为:

灰度形态膨胀即以结构元素g(i,j)为模板,搜寻图像在结构基元大小范围内的灰度和的极大值。腐蚀运算过程则是以结构元素g(i,j)为模板,搜寻图像在结构基元大小范围内的灰度差的极小值。灰度的形态膨胀和形态腐蚀运算的表达式与图像处理中的卷积积分非常相似(即以和、差代替连乘,用最小、最大运算代替求总和)。

灰度形态学开运算的定义为:

开运算是采用相同的结构元先做腐蚀再做膨胀的迭代运算。闭运算是采用相同的结构元先做膨胀再做腐蚀的迭代运算。开运算和闭运算的基本作用是对图像进行平滑处理:开运算可以去掉图像中的一些孤立子域和毛刺,闭运算可以填充一些小洞和将2个邻近的目标连接起来。

在形态算法设计中,结构元素的选择十分重要,其形状和尺寸的选择是能否有效地提取信息的关键。一般情况下,结构元素的选择按照下面原则进行:

(1)结构元素必须在几何上比原图像简单,且有界。

(2)结构元素的凸性非常重要,一般选择凸性子集。

2 灰度形态学滤波器的硬件实现

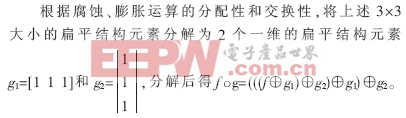

2.1 结构元素选择及简化[3]

本文所述形态学滤波的目的是检测256×256大小12位灰度图像f中的弱小目标,选择3×3大小的扁平结构元素和原始图像做开操作,其结构为:

2.2 电路原理设计[4][5]

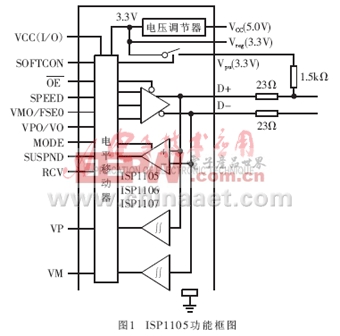

输入图像f与结构元素g1腐蚀就是求f中每行相邻3个象素的灰度最小值。对于1幅静止图像,可以采用1个1×3的窗体从图像第1行第1列开始,自左向右滑动,依次取出窗口内的3个象素灰度值,比较得到灰度最小值并按顺序存储。第1行做完后,再在第2行滑动,直至图像的最后1行的最后3个象素。存储后的图像即为f与g1腐蚀的结果图像。对于实时串行输入图像,只需让图像灰度数据流从1×3的窗体通过,取出窗体内的3个象素灰度值,比较后得到的最小值数据流就是腐蚀后的图像灰度数据。

求3个数的最小值可以先求2个数的较小值,将结果再与第3个数比较即可得到最小值。设计的关键是如何利用第1组数据的中间结果快速完成第2组数据的比较。针对图像是串行输入流以及FPGA内部资源足够丰富的特点,设计了二级流水比较器,其逻辑框图如图1所示。图像第1行第1列的灰度值输入后锁存到12位的触发器,待第2个数据输入后与之比较,较小值锁存到中间的12位触发器,而第2个数据存储到左边的12位触发器。当第3个数据输入后与前2个数据的较小值比较,得到第1组数据的最小值,同时第1组数据中的第2个值作为第2组数据的第1个值,将与第3个数据(第2组数据的第2个值)比较。这样,图像数据输入到1×3腐蚀单元,2个象素周期之后即可得到最小值输出数据流。

将图1中的12位锁存器替换深度为256字节的FIFO,即可得到1×3腐蚀逻辑框图。与1×3腐蚀过程类似,f与g1腐蚀的最小值数据流输入到1×3腐蚀单元,2行延迟时间之

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)