基于FPGA的数据中继器设计

1 前言

高速以太网可以满足新的容量需求,解决了低带宽接入、高带宽传输的瓶颈问题,扩大了应用范围,并与以前的所有以太网兼容。全双工的以太网协议并无传输距离的限制,只是在实际应用中,物理层技术限制了最大的传输距离。不过可以通过使用高性能的收发器或链路扩展器来延长以太网链路的长度。但是面向流量高达数十G的高速以太网中,如何快速、可靠地实现数据的转发与链路延伸并不是一件很容易的事情。尤其是高速以太网中,对设备时延非常敏感,因此要求数据中继设备处理速度有足够的快、同时还能够对转发的数据进行简单分析与处理,才能实现高速、可靠的数据转发功能。另一方面,在10G以太网标准出台之前,就已经有多家厂商推出了基于10G以太网标准草案的10G以太网设备。国外厂商如Foundry、Cisco、Enterasys、Extreme、Forcel0、Nortel、A1catel、Juniper、Avaya、HP、Riverstone等公司纷纷推出了10G以太网设备,国内几家著名的通信设备制造商,像华为、港湾也研发出具有自主知识产权的10G以太网产品。不同公司的产品、设备在对协议实现的一致性、互操作性、稳定性、成熟性等方面都有所不同,因此要设计并实现一个可靠、高速数据中继器必须深入研究高速以太网标准,并充分考虑其设计的灵活性,因此本文提出了一个基于FPGA的高速数据中继器设计方案。

2 高速数据中继器功能分析

高速数据中继器主要需完成以下功能是对外部光纤链路发送过来的高速、大量数据处理,主要包括有: 10G以太网的物理层处理。包括将10Gbps光信号转换为电信号和将10Gbps高速串行数据转换为低速率的并行数据,便于上层处理;10G以太网的链路层处理。包括对10Gbps数据进行PCS解码和MAC控制的链路层处理,最后输出完整的MAC帧;对MAC帧格式进行判断来识别其中封装的上层数据是协议报文还是数据报文;对IP数据报文进行查表处理,看是否有发往本机的IP报文;将需要上交到转发进行深层次IP层处理的数据报文封装成内部数据报文格式并上交;将需要上交到板极处理机的协议报文和发往本路由器的IP报文封装成内部协议报文格式并上交。

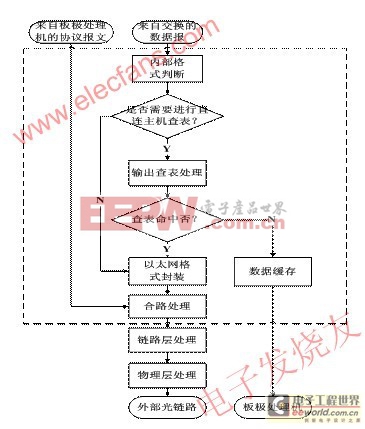

数据中继器对需要转发出去的数据需要完成如下处理:对交换发送过来的数据报文进行内部格式判断,决定是否进行查表处理;对不需要进行查表的IP报文直接从内部头中提取目的MAC地址;对需要查表的IP报文进行查表处理,若查表命中则返回目的MAC地址,若不命中则将该数据报文上交到板极处理机;对得到目的MAC地址的报文进行以太网格式封装;对板极处理机下发的协议报文和封装好的以太网帧进行合路处理;10G以太网的链路层处理。包括对MAC帧进行MAC控制链路层处理和PCS编码;10G以太网的物理层处理。包括并/串转换和电/光转换。其处理流程如图一所示

图 一:高速数据中继器数据处理流程

3 方案的选取与实现

从以上输入处理和输出处理流程来看,物理层和链路层的功能可以通过选择相应的商用器件来实现,实现起来并不复杂;但图1中虚线框内的处理功能是在10Gbps的高速率下进行的,实现起来比较困难。目前在高速数据处理中,能完成这部分功能的处理器件可分为固定功能器件和可编程器件两种,其中固定功能器件主要指ASIC(Application Specific Integrated Circuit),可编程器件又有FPGA(Field Programmable Gate Array)和NP(Network Processor)两种,下面对这三种器件进行比较。

首先能够同时提供极高转发性能和较低成本的只有ASIC芯片了。ASIC的硬件资源最为丰富,处理能力是NP不能比拟,万兆核心层设备采用ASIC是对于性能的一种保障。但是它的先天不足也是无法回避的,由于ASIC的固定特性一直无法解决路由器对多业务支持的需求,ASIC芯片一旦产出后,其原有的功能无法添加,也可以把业内目前需要的功能都做在ASIC里面,但是现在主流的很多技术如MPLS、QoS等都是只停留在草案阶段,还未标准化,所以现在就做死在ASIC里面显然是有很大风险的。由此可看出,ASIC可为任何固定功能提供高性能,但却几乎没有灵活性和可扩展性。第二种NP,目前网络处理器(NP)技术是业内非常受欢迎的技术之一,NP技术本身就是通过厂家自己编写微码的方式对网络协议处理进行优化,通过内置微引擎的方式实现加速处理,性能是CPU无法比拟的。这样的结构注定了NP就比ASIC拥有更多的灵活性,对新增业务的支持能力永远都比ASIC强。但是NP也有其自身不能克服的缺点,NP的硬件资源对比ASIC肯定还是有很大差距的,所以其在处理海量多业务时转发性能下降很快,不能达到线速。

第三种是FPGA,FPGA对任何高速并行数据处理都非常理

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)