基于FPGA的嵌入式脉象采集仪硬件电路设计

时间:12-27

来源:互联网

点击:

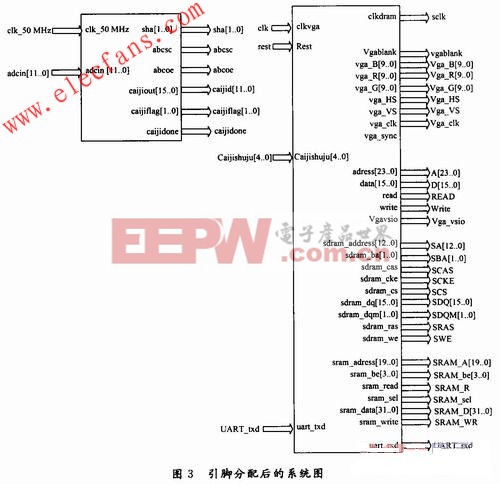

EPCS控制器、FLASH控制器、定时器、VGA控制器、RS 232控制器、脉象采集控制器等。除脉象采集控制器没有现成的IP核可用,需开发控制时序外,其他控制器采用Altera公司提供的IP核。 SoPC系统生成完成后,在QuartusⅡ下建立原理图窗口,调用设计好的NiosⅡ系统与自己设计的脉象采集系统的控制连接,设计完成后,锁定引脚,进行完整编译。完成后的电路如图3所示。 编译后配置到系统中的FPGA去,后面的工作就是嵌入式操作系统的移植和嵌入式应用程序的开发,这时会利用到该硬件平台。 4 结语 设计出嵌入式脉象采集仪的总体方案,并完成了基于FPGA的脉象采集仪硬件电路设计。根据脉象采集的特点,设计脉象采集部分电路,利用IP核构建了脉象采集的SoPC系统。设计的脉象采集仪具有成本低,功耗低,体积小,便于扩展,使用方便,稳定性高,可靠性高,系统维护方便等特点。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)