PCI总线智能GJB289A仿真卡的设计

虚拟仿真系统模拟GJB289A总线设备,需要收发大量的GJB289A总线数据。传统的处理方式是通过GJB289A总线PCI通讯卡将接收到的数据传输到上位机,由上位机程序对数据进行处理,然后上位机再将处理结果通过PCI卡传输到GJB289A总线上,这种方式影响虚拟仿真系统仿真效率,系统实时性不好。此外,传统的GJB289A总线仿真卡处理器程序固定,不能满足不同处理算法的需要。PCI总线智能GJB289A仿真卡实时处理GJB289A 总线数据,无需将数据转移到上位机,提高数据处理速度,增强了系统实时性。用户能够根据需要,在线加载DSP程序,更新数据处理算法,以适应不同处理算法的需要。增强了仿真卡的灵活性。

1 主要功能及指标

PCI总线智能GJB289A仿真卡主要具备以下功能及指标:

CPU主频:600 MHz,处理速度为9 600 MIPS;

缓存空间:SDRAM空间为16 MB;

PCI接口:总线宽度32 b、速率33 MHz;

GJB289A接口:双冗余模拟收发,具备RT/BC/MT,传输速率为1 Mb/s;

在线加载DSP程序。

2 硬件设计

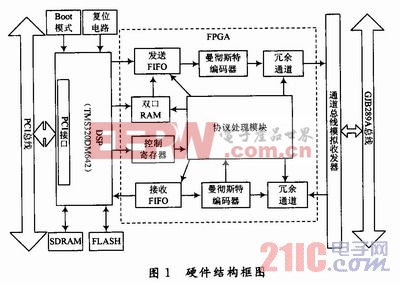

由分析设计要求,在此提出基于TMS320DM642为核心的硬件结构设计:包括DSP及外围电路设计、GJB289A接口逻辑设计、GJB289A总线模拟收发器设计。

2.1 DSP及外围电路设计

TI公司的TMS320DM642是一款主频为600 MHz,32位定点的高性能DSP,片内集成PCI2.2协议模块,支持主/从模式的DMA数据传输。相较于采用专用PCI接口芯片或者FPGA等方式实现,开发方式简单,成本低。

DM642通过EMIFA与SDRAM和FLASH芯片相连,其中2片64 Mb的SDRAM,作为仿真卡的数据缓存空间,FLASH作为程序空间。通过设置Boot模式选择程序从PCI接口还是EMIFA接口加载。当从PCI接口加载时,用户可以动态加载DSP程序,当从EMIFA接口加载时,用户可以将固化好的程序写入FLASH中,由Bootloader引导程序的自启动。

2.2 GJB289A接口设计

GJB289A-97总线是国内在研究为人熟知的MILSTD-1553B总线的基础上制定出来的国家军用标准,全称“数字式时分制指令/响应型多路传输数据总线”,由于其具有极高的可靠性,因而在航空、航天、军事等领域的电子联网系统中得到广泛应用。目前GJB289A协议模块较多由国外的高级 1553B协议处理芯片BU61580实现。在此GJB289A接口协议模块由FPGA逻辑实现,代替原有的协议芯片,节约了系统成本,增加了设计的灵活性。

FPGA逻辑包括曼彻斯特编解码单元、协议处理模块、数据缓冲FIFO、寄存器控制等。逻辑框图如图1所示。发送数据时将已有的并行数据在系统的控制下,经过并/串转换,转换为并行的曼彻斯特编码,依次以符合1553B协议的消息的方式发出。在BC或者RT模式下接收数据时,模拟收发器接收曼彻斯特Ⅱ编码的串行数据,通过曼彻斯特解码器实现同步时钟的提取,同步头检出,数据检出,曼彻斯特Ⅱ码错误检出,奇偶校验,位/字计数以及数据的串/并转换功能。

2.3 模拟收发器设计

模拟发送器是将FPGA输出的TTL电平信号转换为满足协议要求电气特性的信号传输到电缆上,并提供一定的功率使发送信号顺利被接受方正确接收。模拟接收器是将在总线电缆上双极性电平的信号转换为可以直接接入FPGA的TTL电平信号,且信号的失真应控制在一定的范围之内以使得通信过程正确。目前GJB289A总线模拟收发器较多由国外的HI-1573总线驱动芯片实现,在此设计了模拟收发器电路,可以代替1573芯片。模拟发送部分电路如图2所示,由FPGA直接生成的TTL电平信号从电路的左端输入,输入的信号为单极性的曼彻斯特Ⅱ型编码,信号差分输出。图中的两个PNP型三极管工作在开关状态,R1为基极偏置电阻,R2为集电极负载,二极管起保护作用。右端的隔离变压器将信号放大输入到总线电缆。总线驱动器的接收部分电路如图3所示,总线电缆上的信号从右端的隔离变压器输入,通过隔离变压器电平转换后到达高速比较器,信号高于门槛电压时比较器输出高电平;信号低于门槛电压时比较器输出低电平。最终变为两路TTL电平的差分信号输入FPGA中做进一步处理。

TI公司TMS320C6000系列DSP程序主要的加载方式:一种是由EMIF接口引导程序加载,程序代码、数据存放在外扩的FLASH中,这种方式加载的DSP程序是固定的,不能支持在线更新;另一种是由PCI接口引导,主机通过PCI接口可以访问DSP片内片外存储单元,将程序代码写入DSP片内 RAM区,复位DSP时,程序即开始从地址O执行。这种方式可以在线加载DSP程序,更新处理算法,满足系统设计要求,所以本系统采用PCI接口加载方式。

3 DSP程序在线加载方法

用户在主程序框架内添加算法函数,再通过上位机软件,自动调用T

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)