基于 TMS320DM6446 的 H.264 编码器的设计与优化

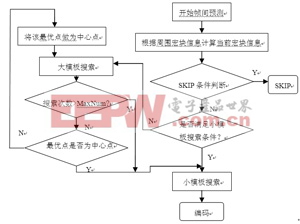

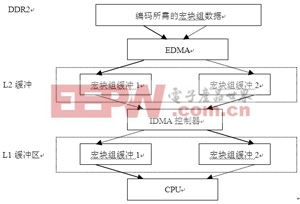

的大模板搜索环节。优化后的菱形算法的流程如图3所示。 图3 优化算法流程图 2 对DSP数据搬移的优化 C64x+在外部存储器与内部存储器之间的数据传递可以通过增强型DMA(EDMA)实现。EDMA传输的发起方式有三种,包括手动触发方式、外设事件发起方式及QDMA模式。在编码算法中,每处理完一组宏块就要向CPU提出DMA传输申请,因此采用QDMA模式的传输发起方式更适用于编码算法。 DSP核对两级内部存储器L1和L2的访问速度也不同,如果将外部存储器的数据直接通过EDMA传入L1D和L1P,这样的传输方式虽然较快,但需要分配比较大的L1 SRAM,这意味着L1的Cache就会变小,过小的L1 Cache会影响L2和外部内存中的代码和数据的效率。出于上述考虑可以将L2作为L1与外部存储器之间的数据过渡区。L1和L2之间的数据传递采用C64x+新引入的IDMA,其原理跟EDMA相似,实现两个内部存储器的高速数据传递。 为了使EDMA可以不间断的实现数据的搬移,本文采用了二级乒乓传输的方式,首先在L1 SRAM和L2 SRAM中开辟两个缓冲区,CPU在处理一个当前宏块组数据之前先处理EDMA和IDMA的传输申请,当CPU编码完一个宏块组时IDMA已将数据搬移至离核最近的L1缓冲区,当CPU继续处理下一个宏块组前再次处理EDMA和IDMA的传输申请。如此以乒乓传递的方式搬移数据可以保证CPU处理数据时最短的等待时间。图4为L1、L2及外部存储器DDR2之间的数据传入示意图。 图4 存储器数据传递流程图 3 优化结果及分析 结束语

视频编码需要处理较大的数据量,如一帧CIF格式的YUV数据约有150KB,而H.264除了要存储当前帧的信息外还必须存储重建帧和参考帧的信息,为此必须使用DM6446的片外存储器,也即DDR。但是DSP的CPU对不同的存储器的访问速度是不一样的,访问速度最快的是离DSP核最近的L1P和L1D,其次是二级缓存L2,访问速度最慢的是DSP的片外存储器。DSP对不同的存储器的访问速度相差数倍。为了提高编码器的运行效率,节省DSP核对各个模块访问所消耗的时钟周期,需要启用DSP的DMA作为数据在两个存储器之间的传输通路。DMA的的特点是可以在不需要CPU干预的情况下,在后台执行数据的高速传输,能够有效减轻CPU的负荷。

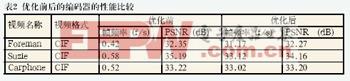

表2为优化前后的H.264编码器对三个测试序列在DM6446上编码后的结果比较。在表2中,优化后的帧频率比优化前有了较大幅度的提高,这是由于对编码器的运动估计模块进行优化后,有效减少了这一模块所消耗的时钟周期。而对DSP数据搬移方式的优化,减少了DSP核等待数据搬入所消耗的时钟周期。表中PSNR的值在优化前后并没有明显变化,说明优化后编码质量未受大的影响。

本文结合DM6446的硬件结构特点,将H.264编码器在DM6446中成功实现,并对编码器运动估计模块及DSP在编码时的数据搬移进行了优化,取得了初步的效果,基本可达到CIF格式序列的实时编码要求。由于DM6446具有DSP和ARM9的双核构架,ARM端负责对整个视频解决方案的控制和对编码算法的调用,因此,下一步的工作重点为实现在ARM端对优化后的编码算法进行合理的调用和控制。

编解码器 相关文章:

- 带DSP功能的超低功率音频编解码器帮助解决音频方案挑战(05-04)

- TMS320C54xx与TLV320AIC24型编解码器接口(05-21)

- 基于DSP的超低功率音频编解码器帮助解决音频方案挑战(01-14)

- 5mW 三洋推全球最低功耗音频处理芯片(09-12)

- 基于ARM9的嵌入式3G无线视频监控系统设计(02-18)

- 基于MSP430单片机和DS18B20的数字温度计(02-01)