基于 TMS320DM6446 的 H.264 编码器的设计与优化

2003年发布的H.264视频压缩编码标准在一定程度上解决了要在尽可能低的码率下获得尽可能好的图像质量这一问题。在相同的重建图像质量下,H.264能够比H.263节约50%左右的比特率,此外H.264还增强了其对网络的适应性,差错的恢复能力,使其非常适用于数字视频存储、IPTV及手机电视等视频质量要求高而信道传输环境不稳定的场合。

由于加入了多模式位移估计、基于4×4块的整数变换等多种新的算法,使H.264算法本身的复杂度大幅增加。因此本文采用基于TI的TMS320DM6446的DAVINCI_EVM平台作为算法的硬件平台,提出针对达芬奇平台对H.264编码器进行优化,在不降低编码质量的情况下提高程序运行效率,降低运算复杂度的一个实现方案。

H.264编码器的算法流程

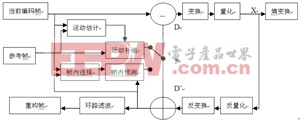

H.264编码器结构如图1所示,输入的Fn为当前帧或场,编码器以宏块为单位进行处理,每个宏块可以选择帧内或者帧间预测两种编码方式。如果采用帧内编码模式,其预测值PRED(图中为P)是由本帧之前已经经过编码、解码、重建的一些样本点生成。而如果采用帧间模式,则P由一个或者多个参考帧的运动补偿预测生成。预测值P和当前块相减后,产生一个残差块D,经块变换、量化后产生一组量化后的变换系数X,再经熵编码,与解码所需的一些信息一起组成一个压缩后的码流,经NAL供传输和存储用。

图1 H.264编码器结构

编码硬件平台概况

本文采用的达芬奇数字视频评估模块DVEVM(Digital Video Evaluation Module)是TI提供的用来评估DaVinci技术和DM644x体系架构的评估模块,是强调片上能力的一个很好的参考平台。其硬件资源包括TM320DM6446的DSP和ARM9的双核芯片、128MB的SDRAM、16MB的NAND Flash以及丰富的外设接口。

TM320DM6446中用于编码器具体实现的C64x+ DSP的时钟频率达到600MHz。C64x+ DSP的内部存储器的配置包括32KB的程序存储器L1P、80KB的数据存储器L1D和64KB的二级缓存L2。图2为TM320DM6446中DSP端的核心C64x+的结构原理图。

编图2 C64x+结构原理图

码器在TM320DM6446上的实现

由于DSP平台与PC平台的差异性,必须对PC上开发的编码器程序进行结构上的调整,并进行合理的内存分配才能在DSP平台上正常的运行。主要实现步骤如下。

1 编码器C语言结构调整

PC平台上用C语言实现的编码器在DSP平台上的编码帧率(fps)非常低,平均2秒才能编完一帧,其主要原因是无法利用DSP的并行处理机制。因此针对C64x+的特点,将程序中对流水线操作影响较大的的循环拆分成若干小循环实现。对编码器运行速度影响较大的模块如sad的计算,DCT变换等采用CCS自带的图像库以提高编码效率。

2 DSP端的内存配置

由于视频编码的数据存取量较大,而 DAVINCI_EVM提供了256MB的外部存储器DDR2,因此通过对DSP/BIOS的设置将外部存储器设置为DDR2,并将可执行的C代码及C代码的堆存入外部存储器中。

3 对DSP端的BOOT的设置

由于TM320DM6446采用双核的设计,ARM端只负责对整个工程的控制而不参与编码算法的具体实现。为了保证编码算法能在DSP端无中断的全速运行,需要对ARM端进行屏蔽,并通过对DAVINCI_EVM跳线的设置使DSP端自BOOT。

通过以上步骤编码器效率虽然有所提高,但仍无法满足实时性的要求,因此必须结合DM6446本身的特点对编码器算法进行进一步的优化。

编码器的优化

本文对H.264算法的优化主要有两个方面:1)对算法中耗时较多的运动估计模块进行优化。2)对DSP的数据搬移进行优化。

1 对编码器算法运动估计模块的优化

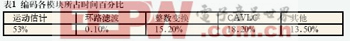

由于DSP硬件资源有限,因此有必要对H.264编码器中所耗时间较多的模块进行优化,表1为H.264各模块复杂度比较。

由表1可见运动估计占了一半左右的时间,运动估计复杂度高的主要原因是采用了全搜索算法,虽然精度非常高,但带来了大量的计算量。针对这一问题,本文在已有的快速算法菱形搜索算法基础上进行进一步的优化。

为了减少静止宏块被编码以及大模板搜索所带来的运算量,首先在用菱形算法进行运动搜索之前以待编码宏块周围已编码宏块的运动矢量信息及SKIP状况为依据预测当前宏块是否使用SKIP模式编码。当待编码宏块为非静止宏块时,再根据周围已编码宏块的SAD值预测当前宏块的运动剧烈程度,若是运动平缓的宏块则直接使用小模板进行搜索。只有当待编码宏块被判定为剧烈运动的宏块时才进行大模板搜索。由于多次的大模板搜索循环带来较大的计算量,因此在进行大模板搜索之前首先根据周围宏块的信息对最大搜索次数MaxNum进行预估值,当大模板的搜索次数大于MaxNum时直接跳转至小模板搜索。此流程设计可使静止宏块和运动平缓的宏块不进入运算量大

编解码器 相关文章:

- 带DSP功能的超低功率音频编解码器帮助解决音频方案挑战(05-04)

- TMS320C54xx与TLV320AIC24型编解码器接口(05-21)

- 基于DSP的超低功率音频编解码器帮助解决音频方案挑战(01-14)

- 5mW 三洋推全球最低功耗音频处理芯片(09-12)

- 基于ARM9的嵌入式3G无线视频监控系统设计(02-18)

- 基于MSP430单片机和DS18B20的数字温度计(02-01)