基于DSP的超低功率音频编解码器帮助解决音频方案挑战

便携式消费电子设备制造商目前面临着开发低成本、高性能、功能丰富而且电池寿命更长的音频解决方案的艰巨挑战。同时,制造商也被迫缩短开发时间以便领先一步推出新产品。随着最近带嵌入式迷你DSP和强大图形编程工具的超低功率编解码器的成功推出,制造商现在已经能够满足这些复杂要求。

这些器件具有超低功耗和DSP处理能力,能为那些需要独立编解码器的系统、以及采用基带处理器或带模拟I/O的应用处理器芯片的系统提供低功率音频解决方案。其图形化编程环境和丰富的软件库使得应用程序的开发时间缩短到传统编程环境所需时间的一小部分。

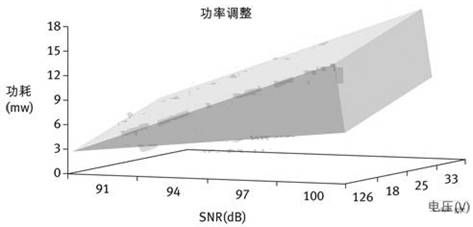

在低功率操作方面,这些新一代超低功率编解码器能使模拟和数字内核在1.5V到1.8V的单电源下工作。通过使数字内核的工作电压低至1.26V,从而可能进一步降低功耗。许多器件有低功率工作模式。然而,新增的功率调整功能还能让设计师根据录音与回放路径中使用的各种配置和处理条件调整器件功率。设计师可以根据输入通道数量、输出驱动要求、采样率、想要的输入输出信噪比(SNR)性能、以及使用的处理功能对功率进行动态优化,从而实现功耗的最小化。

通过这种方法可以灵活调整编解码器功耗,从而为不同的音频再现模式(按键音、消息音、语音通信和音乐再现)、不同的I/O配置(听筒或耳机操作)和不同的信号处理要求(低噪声或高噪声通信环境)提供最佳性能,如图1所示。功率调整控制还允许进行额外配置,如配置成较少转换的模拟旁路工作模式、PLL或PLL-less的工作模式、D类或AB类耳机驱动模式等。这些配置控制通过I2C或SPI总线进行管理。

功率调整功能使便携式音频设备的电池寿命产生显著延长。低功率操作模式允许带信号处理功能的超低功率编解码器的功耗在处理按键/消息音时低于5mW,在处理8kHz或16kHz的语音通信时低于7mW,在进行最高质量的44.1kHz立体声耳机音乐再现时低于10mW。

在一个芯片中整合超低功率数据转换和低功率信号处理功能可以显著节省包含应用处理器和编解码器的传统系统架构的功耗。在这些架构中,超低功率编解码器可以执行应用处理器的一些甚至全部音频处理功能。

含基带或应用处理器芯片的系统一般都具有模拟输入和/或输出功能。带信号处理功能的编解码器可以为新增特性或功能提供低成本、短开发周期的解决方案,无需重新编程或替换现有的基带或应用处理器。

带嵌入式迷你DSP的新型超低功率编解码器是用于延长电池寿命的强大工具之一。这些器件及其强大的图形化编程工具可以为各种便携式音频处理和通信系统架构提供低功率音频解决方案。在立体声回放时功耗可低至2.4mW。编程是在图形化软件环境中完成的,因而也简化了制造商的编程过程。

便携式消费电子设备市场竞争非常激烈,更新速度也非常快。快速上市时间和极低功耗器件可以帮助制造商缩短他们的设计周期,并开发出有特色的产品。带嵌入式DSP和能快速编程的图形化软件开发环境的极低功率音频转换器将提高制造商的竞争优势。

图1:功耗随SNR和电压增加而增加。用户可以根据应用和系统要求调整功率。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)