使用EYEQ特性实现高速串行IO的最佳相位接收判决

现有的很多高速串口协议,都要求很低的误码率,比如CEI-6G-LR(6.375G, 40英寸走线)就要求1E-15的误码率。为满足此类低误码率要求,ALTERA高端的FPGA STRATIX IV系列,提供了片上信号质量检测电路(EYEQ),帮助客户在高速串行IO接收处找到最优的采样位置。

通常眼图的张开度是用来衡量接收端信号的质量。片上信号质量检测电路(EYEQ)就是一个调试诊断工具来帮助分析接收的数据路径,包括接收端的增益,噪声水平。

原理

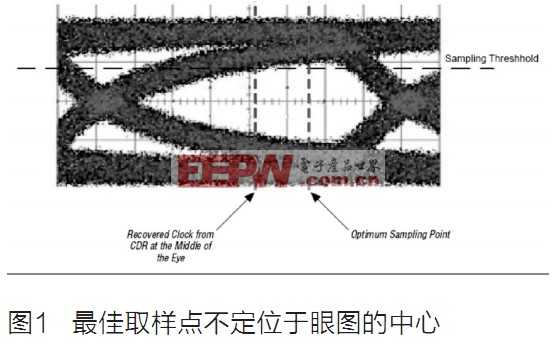

缺省情况下,CDR恢复时钟是在眼图的中间位置采数据,如图1的红色虚线位置,但是根据这个眼图的张开程度,最佳采样位置应该是在绿色虚线部分。只有在绿色虚线位置,眼高最大,这样采样到的数据才具有最低的误码率。

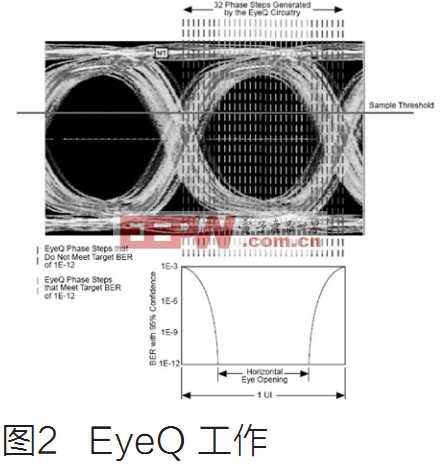

EYEQ电路在一个完整的信号周期(UI)中,将采样时钟放到32个相位上,用户可以根据每个不同相位时的误码率,找出最佳采样相位。如图2所示。

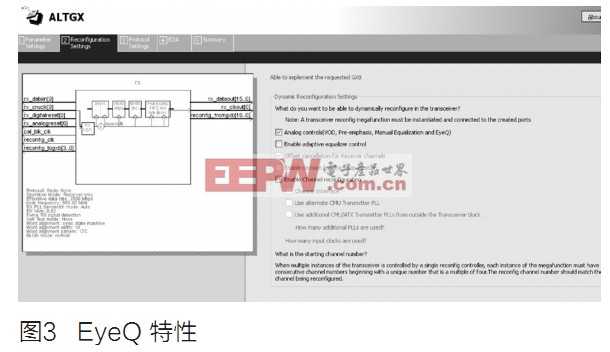

用户使用EYEQ功能要在ALTGX和ALTGX_RECONFIG两个模块中打开EYEQ的特性。

首先,在使用QUARTUSII软件生成TRANCEIVER时,按照图3,打开EYEQ特性,

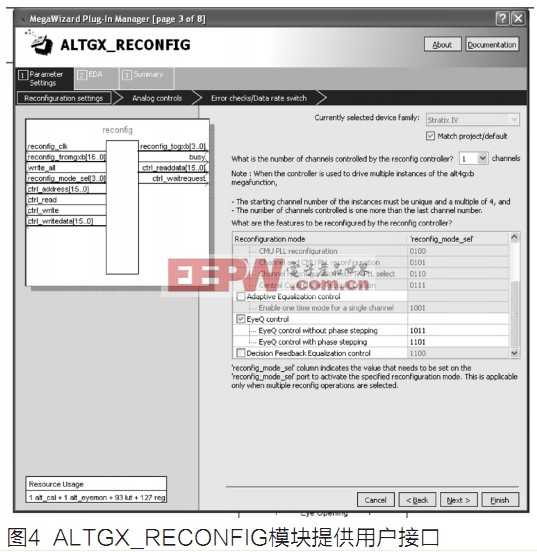

然后,在生成RECONFIG模块的时候,选择eyeq control, 如图4所示。

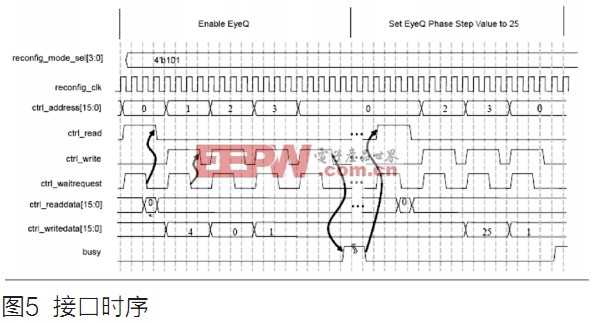

ALTGX_RECONFIG模块提供了一套用户接口,包括读写信号,读写地址,读写数据等。用户可以通过这个接口实现相位的调整,这个接口的时序如图5所示,这个例子是将采样时钟相位调整到25上。

结语

本文中,我们介绍了如何使用EYEQ特性来实现高速串行IO的最佳接收。EYEQ是一种实用的调试工具来衡量眼图质量和调整采样位置,嵌入在ALTERA的FPGA器件中,并且不会另外收取费用。相比较价格昂贵的高速实时示波器和采样示波器,EYEQ不失为一种方便、低廉的测试方法。

高速串行IO一直是ALTERA的技术优势领域,EYEQ只是其中的一部分。我们相信,我们在此领域的优势可以为客户带来更大的价值。

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)