让生物识别技术成为FPGA动态部分重配置功能的“杀手级”应用

别特性,并作为识别算法的输入,如图 2 所示。

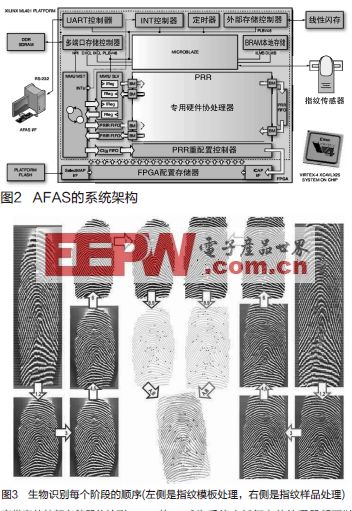

作为计算单元,FPGA 被划分为两个区域,一个是静态区,由完整的多处理器 CoreConnect 总线系统构成;另一个是可重配置区,用于根据需要放置定制的生物识别协处理器或IP(知识产权),以执行识别算法的各种顺序任务,并随处理的进展进行复用。多处理器 CoreConnect 总线系统主要由赛灵思 MicroBlaze 处理器及其它标准外设构成,同时还拥有一个链接至 ICAP (内部配置访问通道)端口的重配置控制器。

如图1所示,所有的处理任务都按照顺序执行的次序从 0(静态)到 B 进行枚举。定制的硬件协处理器负责在 PRR (部分重配置区域)中实现所有的任务,由 MicroBlaze 在软件中完成的指纹采集过程除外。

软硬件特定的划分是由于扫描传感器需要 5μs的积分时间来获得连续的图像条(SLICE)。这种速度下无需采用定制的硬件协处理器,采用MicroBlaze软件采集和重构图像不仅速度足够,而且更简单经济。

图像采集按每个 SLICE 5μs的速率采集 100 个SLICE,每个 SLICE 的大小为 280x8 像素。每两个连续的图像 SLICE 之间的像素重叠部分交由软件进行探测,从而完成图像的实时重构。

由于实时的要求,剩余的任务我们交由 FPGA 的 PRR 的定制硬件协处理器来实现。一旦每个特定的任务完成之后,位于器件静态区的重配置控制器在 MicroBlaze 处理器的控制下,载入下一个任务的工作模块。重配置控制器通过 ICAP 接口将新模块的配置数据从 DDR-SD M 中直接传输到内部的 FPGA 配置存储器中,从而完成此项任务。

值得一提的是,我们使用的是静态区和可重配置区之间基于 FIFO(先进先出)存储器和触发寄存器构成的标准界面。这样我们就可以在 PRR 中开发标准的生物识别协处理器或 IP,而无需理会系统使用的是哪种多处理器总线,无论其是 AMBA、CoreConnect、Wishbone 还是其它均如此,如图 2 所示。这一点具有根本性的意义,因为这样才能确保生物识别算法跨不同平台的标准化和便携性。

重配置控制器

设计高效的重配置控制器是部署面向单一环境 FPGA 的 PR (部分重配置)系统的成功关键。虽然在重配置 PRR 期间,FPGA 的非重配置区域仍然处于工作状态,但 PRR 资源此时并没有处于工作状态,故应尽量加快重配置过程,以便最大限度地降低开销。重配置的时间取决于三个因素:数据总线宽度、重配置频率以及比特流大小。前两个因素与接口特性有关,而最后一个与 PRR 的大小及其中的部分重配置模块 (PRM) 的设计复杂程度有关。

我们的工作实现了一个重配置控制器,其能在运行时将部分比特流以高带宽从外部存储器传输到 FPGA 的片上配置存储器中。在不限制部分比特流大小,同时将外部存储作为共享资源(各种处理器可通过系统总线同时访问)的条件下,仍然可以达到Virtex-4最高重配置带宽。

在系统初始化阶段,部分比特流将在运行中被下载到 FPGA 配置存储中,并从外部的Flash中传输到外部 DDR-SDRAM。该存储器与多端口存储控制器 (MPMC) 相连接,因而成为系统中任何主从处理器都可以访问的资源。可以使用 CoreConnect PLBv46 总线等不同类型的总线连接到 MPMC,这些总线可用作通用系统总线,而赛灵思 Cachelink (XCL) 总线则用于 CPU 的快速指令和数据缓存。系统 CPU (MicroBlaze) 实际上是与这两个总线相连接的。

不过我们的重配置解决方案是建立在新总线基础之上的,即专用于快速链接外部 DDR-SDRAM 存储库和 ICAP 接口之间的原始端口界面 (NPI)。作为我们重配置控制器的组成部分,我们设计了可用来处理 NPI 协议的主系统存储管理单元 (MMU)。外部 DDR-SDRAM(部分比特流)和 ICAP 原始之间的连接需要经过一个内部 FIFO 存储器。借助这种方法,我们可以实现两个不同的定制界面,它们各自拥有独立的数据总线大小和速度,一个与 NPI 协议耦合,另一个则与 ICAP 协议进行耦合。

FIFO 的写入端口与 NPI 相连接,并使用 64 位数据总线;而 FIFO 的读取端口则连接到 ICAP,使用 32 位数据宽度,这是 ICAP 在 Virtex-4 器件中的最高数据宽度。FIFO 的读取端口和写入端口(在 NPI 侧和 ICAP 侧)的运行频率为 100MHz。为使传输时延降至最低,主系统 MMU 负责以 64 字(32 位)突发传输向内部 FIFO 传输配置数据,从而完成模块的重配置。这是可接受的最大突发长度,因而所有的重配置数据传输都能够以最低突发时延完成。在另一侧,只要 FIFO 不为空,重配置控制器就能读取已存储的 FIFO 数据,并将其以 32 位格式传输给 ICAP 接口。重配置控制器(就是

- 八大角度让你读懂指纹识别(07-19)

- 指纹识别中的图像处理研究------指纹图像的特性分析 (一)(11-20)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)