全景图像实时展开在FPGA上的实现

摘要:全景摄像机可以使用一个摄像头获取周围360°的环境信息,与以往的多摄像机获取方法相比大大节省了硬件资源,并且在还原全景图时避免了多画面拼接产生的“鬼影”问题。但由于反射式全景摄像机获取的画面为极坐标视图,为适应人眼观察习惯需要对其进行展开。本文在FPGA上实现了对反射式全景图像的实时展开,在27MHz系统时钟的驱动,生成122万像素的展开图像达到了21.97fps的帧速。

关键词:全景摄像机;FPGA;嵌入式系统

目前,全景技术的研究主要将注意力集中在集合变换算法和镜头矫正算法的改进,对实时性问题研究较少。本系统利用FPGA对圆形极坐标图像进行实时展开。

系统总体设计

本系统在以EP2C70 FPGA芯片为核心的DE2-70开发板上实现,系统主要模块如图1所示。

(1)视频采集模块:将ADV7180芯片输出的数字视频信号采集到SDRAM中缓存,并获取相应的控制信号。

(2)VGA控制模块:将已经处理好的数字视频信号输出到ADV7123,之后进入VGA显示器进行显示,并生成VGA控制信号和坐标信号。

(3)展开算法模块:利用VGA控制模块产生的坐标信号对极坐标数字视频信号进行展开操作,生成矩形视频信号。

系统模块设计

根据系统框图,本系统可分为以下几个主要模块:视频采集模块、展开算法模块和VGA控制模块。系统时钟为ADV7180产生的27MHz像素时钟,保证了采集与处理的同步进行。

视频采集模块

视频采集模块接收由ADV7180芯片串行输出的格式为ITU-R BT.656、分辨率为720×525的数字视频信号,并提取信号中有效像素信息,同时将其转换为分辨率为640×480的数字视频信号,存入SDRAM中,之后,再提取缓存中数据转换为适合VGA显示的RGB信号传输到后续模块。

ITU-R BT.656解码器

ITU-R BT.656协议以27MHz速率复用传送数字视频数据,其顺序是:Cb,Y,Cr,Y,Cb,Y,Cr,?? 其中,Cb,Y,Cr 这三个字指的是同一个像素的亮度和色差信号,之后的Y 对应于下一个像素的亮度。Y、Cb、Cr在传输中数据量的比为Y:Cb:Cr=4:2:2。另外,信号同时包括相应的场、行信号。ITU-R BT.656解码器的目的是将ADV7180芯片产生的ITU-R BT.656协议数据流中的8位像素信息提取出来,并根据协议中的控制信号生成相应的行列扫描信号与像素有效信号。在提取像素信息的同时,将数据存储顺序变换为:Y,Cb,Y,Cr,Y,Cb,Y,Cr??。在存入SDRAM时,偶数地址存储{Y,Cb},奇数地址存储{Y,Cr}。

SDRAM控制器

SDRAM控制器采集ITU-R BT.656解码器输出的像素信号,将其存入DE2-70开发板上的IS42S16160B SDRAM中。系统将其设计为一个四端口控制器,包括两个读口和两个写口,并且使用108MHz时钟驱动SDRAM控制器和SDRAM芯片,保证在分频之后,每一个读写端口的频率为27MHz,与像素时钟同步。

由于ADV7180产生的视频数据流是隔行扫描数据,分为奇数场和偶数场,所以SDRAM控制器除了对数据流进行存储,还要在读取数据时进行去交织操作。SDRAM控制器的双读口设计可以出色地完成去交织任务。在读取数据时,利用VGA的行扫描信号控制这两个读口分别读取:当VGA控制器扫描到奇数行时,由第一个读口读取相应奇数行数据;否则,由第二个读口读取相应偶数行数据。之后,再合并这两个读口读取的数据得到逐行扫描的、分辨率为640×480的视频数据流。

YCbCr到RGB转换模块

本系统的最终目的是将视频流输出到VGA显示器进行显示,而从SDRAM读取得到的数据是YCbCr422格式,不符合VGA显示要求,所以需要将其转换为RGB数据格式。

首先将YCbCr422格式转换为YCbCr444格式。在每一个时钟上跳沿,判断当前VGA列扫描信号,若当前列为奇数,则将SDRAM读口得到的16位YCbCr信号的前8位赋值给Y作为当前像素的Y值,后8位赋值给Cr作为当前像素的Cr值,Cb保持不变;若当前列为偶数,则YCbCr的前8位仍为当前像素的Y值,后8位为当前像素的Cb值,Cr保持不变。这样就保证了输出的Y、Cb、Cr三个信号是当前像素的对应描述信号。

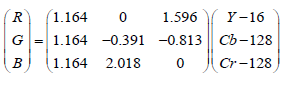

在确定了每个像素对应的YCbCr值之后,就可以通过如下公式计算得到对应的RGB值。

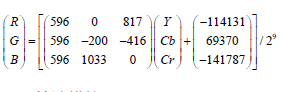

DE2-70上的EP2C70 FPGA芯片内嵌了150个乘法器块,每一个乘法器块可以配置为两个9×9位的乘法器或者一个18×18位的乘法器。所以本系统使用QuartusⅡ中集成的MegaWizard Plug-In Manager配置乘加器模块用于实现YCbCr颜色空间到RGB颜色空间的转换。另外,上述转换公式涉及浮点运算,在Verilog中不易实现,所以将公式中各浮点值左移9位变为整数,从而公式调整为:

???????????−??????????展开算法模块

???????????−??????????展开算法模块

展开

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)