一种高效灵活数字上变频FPGA设计

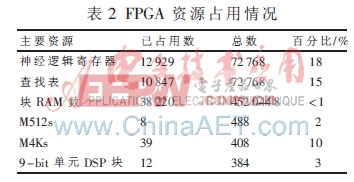

表1中数字上变频器的要求,在Matlab中仿真插值滤波器的参数。本设计采用2插值的补偿滤波器CFIR和4插值的积分梳妆滤波器CIC级联结构。补偿滤波器CFIR不仅起到低通滤波器和2插值的作用,而且具备平滑CIC滤波器的作用。图4是参数R=4,M= 2,N=8时,补偿滤波器CFIR和积分梳妆滤波器CIC级联后的幅频响应,从图中可以看到该幅频响应的混叠抑制达到100 dB。 本文设计的数字上变频系统实现了通带频率1.0 MHz,截止频率1.5 MHz基带信号经过8插值上变频到载频10 MHz的调制信号。该数字上变频占用的主要FPGA EP2SGX90内部资源如表2所示。结果表明,该系统在占用少量资源的情况下实现了数字上变频功能。 5 结果分析

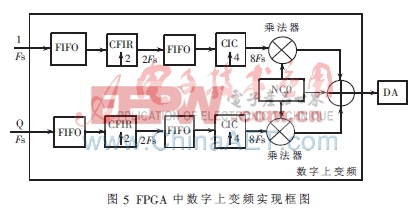

FPGA EP2SGX90具有丰富的IP(Intellectual Property) 资源。利用其FIR IP和CIC IP实现插值滤波,利用NCO IP实现上变频。其中FIR IP系数采用对称结构,这样节省一半的系数存储单元。数字上变频器在FPGA中的实现框图如图5所示。由于补偿滤波器CFIR 和插值滤波器CIC IP核的特点,输入信号不是连续的,因此在设计中需要在二者的输入端添加FIFO。采样率为Fs的基带信号通过CFIR 2插值后采样率变为2Fs,同样该信号再经过4插值CIC滤波器后采样率为8Fs。FPGA采用流水结构,实现信号的实时处理。

为了验证本文设计的数字上变频的性能,数据从数字上变频系统输出后经过AD9747芯片进行数模转换,模拟信号接到示波器上观察到的波形如图6所示。这里使用的是LeCory公司的序列号LCRY0409N01153的示波器。 图中C3对应的是原始基带信号经过数模转化后的模拟信号,C4对应的是数字上变频后数模转化后的模拟信号。

本文研究了数字上变频的原理,以实际工程需要为例介绍了使用FPGA设计数字上变频的过程。采用梳妆滤波器和补偿滤波器级联的结构使数字上变频有很好的内插滤波器特性。同时根据FPGA中CIC和FIR IP核的时序特点,设计了高效流水结构,这对实际的工程设计有重要的指导意义。本文设计的数字上变频具有可编程、信号精度高、系统无杂散动态范围高达100dB的特点,在FPGA中能稳定可靠地运行。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)