可编程模拟器件在接收机动态可重构结构应用

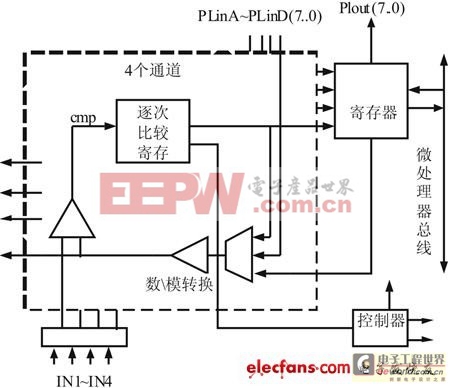

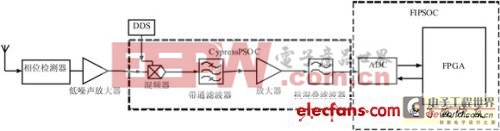

这些DAC实现高达800KHz采样率的ADC(见图4)。 图4 数据转换模块的框图 数据转换模块包含4个8位的逐次比较寄存器(SAR),它可以和内部的DAC联合工作,以获得模/数转换。 每一个通道有一个独立的SAR,它接收逐次比较的结果,并驱动对应的DAC,每一个通道的转换可以独立进行。当转换模块编程为9或10位ADC转换时,相应的SAR形成组:9位ADC时,SAR1和SAR2为一组,SAR3和SAR4为一组;10位ADC时,所有4个SAR形成一组。这时,成组的SAR各自工作1至2个周期,在转换结束时,SAR将其内容寄存在输入/输出寄存器中,并使能中断产生模块。在连续转换模式下,将启动下一次转换。在转换过程中,可编程逻辑模块可以独立发布转换命令,这将给本次以及下一次转换带来错误。在连续转换模式下,这将导致致命错误,因为错误是可以传递的,并将得到不可预料的结果。 其控制部分是一个标准的8051微处理器。复合后,8051核首先对可编程元胞进行配置,配置完毕后可以当作一个通用的微处理器使用。为了更好的支持FIPSOC的动态可重构特性,已对其指令和功能单元做了一些改进。 CypressPSoC器件 Cypress半导体公司的PSoC混合信号架构将可编程的模拟与数字模块同8位微控制器进行了完美集成,这种独特的功能组合使设计人员能够针对各种应用实现无与伦比的灵活性。最新CY8C23x33器件采用8位逐次逼近ADC,能实现高达375Ksps的采样率。此外,该解决方案还具备可实现出色可配置性的26个GPIO,能够快速适应不断变化的特性要求。该器件采用5x5mm的QFN封装,能够最大限度地缩小板极空间。 PSoC器件集成了通过一个片上微控制器进行控制的可配置模拟和数字电路,提供更强大的设计修改功能,并进一步减少元件数量。PSoC器件包括最大32Kb的闪存、2Kb的SRAM、一个带有32位累加器的8x8乘法器、电源和睡眠监控电路,以及硬件I2C通信[2]。 所有的PSoC器件都是可动态重配置的,使得设计人员能够随意在运行过程中改变内部资源形式,使用较少的元件完成既定任务。易用的开发工具让设计人员能够选择可配制程序库元素来提供模拟功能(如放大器、ADC、DAC、滤波器和比较器),以及数字功能(如定时器、计数器、PWM、SPI和UART)。PSoC系列器件的模拟性能包括轨至轨输入、可编程增益放大器和分辨率高达14位的ADC,以及超低的噪声、输入漏电流和电压偏移。 单个PSoC器件可集成多达100个外围部件,在提高系统质量的同时,节省客户的设计时间,缩减板级空间和功耗,并使系统成本降低。 接收机设计 基于以上分析的结果,结合前端硬件电路,为实现一定的认知无线电功能,特设计接收机结构(见图5)。 图5 接收机结构 前端低噪声放大器选用的是ADA4857-1,这是一个超低损耗、低功率、高速运算放大器,在SOIC结构下的3dB带宽可以达到750MHz,其开环增益为57dB,基本满足此接收机对前端低噪声放大器的要求。在搭建电路时尤其要注意电源旁路、寄生电容和外围器件的选择对充分发挥放大器性能的影响[3]。 DDS(直接频率合成器)选用的是1GSPS的AD9858,其使用先进的DDS技术和一个内置的高速、高性能D/A转换器组成数字可编程、完全高频率的合成器,可以产生一个高达400MHz的模拟输出正弦波,完全满足接收机对本振的要求。

- 基于DSP的短波分集合成接收机(09-01)

- 基于DSP的低功耗接收机单边带解调方法(01-10)

- 基于DSP的低功耗接收机单边带解调系统设计方法(06-17)

- 基于导航接收机的DSP外设存储器行进测试技术(09-16)

- 一种CPCI总线结构微波接收机的设计方案(12-21)

- Ka波段接收前端的设计(12-21)