基于FPGA的诱发电位仪完整系统设计

0引言

诱发电位是指对神经系统某一特定部位给予特定刺激后在大脑皮层所产生的特定电活动,对于神经系统功能性异常的疾病有独特的检测诊断能力,也是大脑认知和脑机接口研究常用的技术手段。诱发电位仪通常包括视觉诱发电位、听觉诱发电位和体感诱发电位三种检测功能,其硬件系统核心组成部分包括:刺激信号源、脑电信号放大和数据采集。刺激信号源包括视觉刺激信号(如棋盘格、黑白闪光等)、听觉刺激信号和神经刺激信号,一般采用分离设计。

脑电信号数据采集一般包括模/数转换、数据预处理和数据传输等部分,而模/数转换芯片和主控微处理器芯片的选择主导了整个数据采集系统的性能。在目前的采集系统中,基于单片机的中低端控制芯片功能较弱,逐渐被DSP和ARM或增强型单片机所取代。DSP芯片采用哈佛结构的流水线工作方式,能实现复杂信号处理算法,如文献采用DSP实现复杂的脑电信号采集系统;而ARM适合做事务处理或者中低端应用,如文献中通过ARM处理器建立操作系统实现任务调度。尽管采用DSP和ARM芯片可使系统的运算能力和管理事务的能力得到很大增强,但是构成完整的数据采集系统通常还需要外部逻辑控制器件,尤其不能将数据采集和刺激信号源在单片上集成实现。

由于现代电子技术的飞速发展,可编程逻辑芯片FPGA的集成度越来越高,受到很多厂家和研究机构的关注,利用它的可编程性和可扩展,可将绝大部分的功能集成到FPGA芯片中。如文献采用FPGA实现了脑电信号采集;文献则将盲分离算法ICA在FPGA上实现,能同时对脑电信号进行采集和独立分量分解。

本文针对诱发电位仪的硬件系统设计,提出将信号采集控制、处理、传输、刺激信号产生等功能集成在一块FPGA芯片上的设计方案,并结合ADSl258模/数转换芯片,使得系统具有16通道,每个通道24位采样精度和400 kHz采样率的高性能,而且电路结构简单。

1 系统总体设计

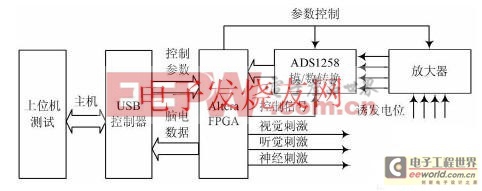

本文提出的诱发电位仪包括了刺激信号源、数据采集和数据传输三大部分。其中核心控制芯片采用Altera公司的FPGA,产生刺激诱发信号源包括听觉刺激、神经传导刺激和视觉诱发刺激,以及实现对外围电路如A/D,USB等模块的控制并在芯片内部集成滤波算法模块;数据采集采用高精度多通道的模/数转换芯片ADSl258将通过放大器放大后的诱发电位信号进行模/数转换并输入FPGA内进行前置处理;数据传输通

过USB控制器Cypress 68013A将诱发电位数据传输至PC上位机,由上位机应用程序实现诱发脑电信号的后期处理、显示、存储等功能。系统总体框图见图1。

图1 系统总体框图

2 FPGA软件模块设计

2.1 FPGA的优势

FPGA即现场可编程门阵列,是在CPLD的基础上发展起来的新型高性能可编程逻辑器件,它既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了普通ASIC设计周期长、投资大、灵活性差的缺点,逐步成为复杂数字硬件电路设计的理想选择。不同于传统的诱发电位仪设计,本文将大部分分立元件实现的功能集成到了FPGA芯片中,实现多种刺激模式和滤波模块以及实现对外围器件的控制,不仅提高了集成度使仪器小型化、便携化成为可能,而且片内模块可反复修改,提高了设计开发效率降低了成本,也可以方便地实现各模块之间的同步。

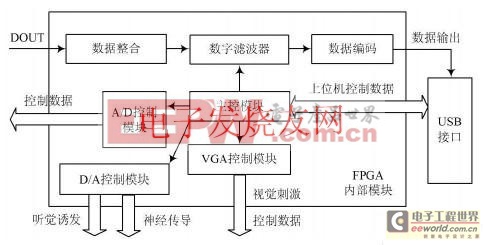

2.2 软件模块整体设计

本设计中,FPGA芯片软件模块包括了诱发电位刺激模块、信号传输控制模块和数字信号处理模块三大部分;由共同的同步信号协同合作,完成诱发电位仪的诱发刺激、信号的传输、数字滤波等核心控制处理功能。FPGA内软件模块框图如图2所示。

图2 FPGA 内部功能结构模块

2.3 诱发电位刺激模块

在FPGA芯片中设计了诱发电位刺激模块,主要功能包括:听觉诱发电位刺激、神经传导刺激和视觉诱发电位刺激。刺激信号主要由脉冲信号进行控制,通过 FPGA芯片可以直接输出脉冲信号和VGA控制信号。听觉诱发刺激信号和神经传导刺激信号可由FPGA输出的脉冲信号经功率放大后产生,在此听觉诱发电位刺激信号为双通道,一路信号产生脉冲信号如PWM(脉宽调制)波,另一路由FPGA芯片内部模块通过DA转换器产生白噪声,而神经传导刺激信号可直接由 FPGA输出PWM脉冲直接驱动电压放大器生成。通过Verilog硬件描述语言,在FPGA中实现诱发电位刺激源信号,并通

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)