Stratix系列FPGA电源方案设计分析

其中,R2是反馈分压网络的上部电阻,R3是FBx与地之间连接的电阻。 两个PWM控制器都使用低端MOSFET导通电阻(RDS(ON))进行电流监控。检测到的电压降与OCSETx脚和地之间的电阻(如图3中R8、R9)设置的门限相比较:

如图1所示,门控逻辑将生成的PWM信号转换为门驱动信号,提供放大、电平移动和击穿保护。FDS6990集成了两个N沟道MOSFET,高端MOSFET的门驱动电压由自举电路产生。选用BAT54HT1肖特基势垒二极管作为自举二极管,正极与VCC_5V相连。BOOT脚与PHASE脚之间的自举电容为高端MOSFET驱动器供电。UGATE为高端MOSFET提供门驱动,LGATE为低端MOSFET提供门驱动。启动时,低端MOSFET导通,使PHASE接地,从而给自举电容充电至5V。低端MOSFET断开后,高端MOSFET通过关闭BOOT和UGATE之间的内部开关,实现导通,从而提供所需的栅极-源极电压来导通高端MOSFET。

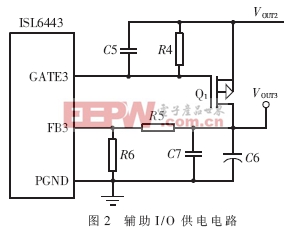

2.1.2 辅助I/O供电电路[4]

根据FPGA系统的不同需求,可能存在不同的I/O标准,因此可能存在多个I/O电压。由于ISL6443集成了一个额定增益为2A/V的线性稳压器,可利用VOUT2(3.3V)为其供电,输出VOUT3(2.5V)作为辅助I/O电压。

如图2所示,GATE3是线性稳压器的漏极开路输出,FB3与反馈电阻分压器相连,提供电压反馈信号。Q1选用了IRF7404 P沟道MOSFET。当PWM的输出升高且超过了MOSFET调整器件的门限时,线性稳压器的输出将跟踪PWM电源。PWM和线性稳压器的输出之间的电压差分等于负载电流和MOSFET导通电阻(RDS(ON))的乘积。

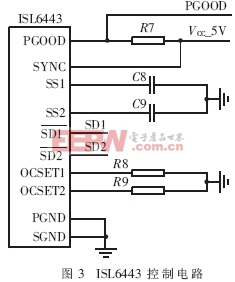

2.1.3 ISL6443控制电路[4]

控制电路主要用来实现ISL6443的过流保护、反馈回路补偿、多个控制器的同步等功能。

如图3所示,PGOOD为漏极开路输出,用来监控输出电压的状态。当任一PWM的输出超过相应额定电压的10%,或线性稳压器的输出小于额定值的75%时,PGOOD变为低电平,从而使转换器输出受到过载、短路和欠压保护。另外,SS1和SS2脚为相应的PWM控制器提供软启动功能。当软启动开始时,由于有5μA的电流注入外部电容,激活的PWM通道的SS脚上的电压呈斜坡上升,输出电压跟随软启动电压变化。当SS脚上的电压达到0.8V时,激活的PWM通道的输出电压达到规定值,从而完成软启动过程。SD1和SD2脚为相应的PWM输出提供使能或禁用功能,高电平启动,低电平输出禁用。

ROCSET=

其中,IOC是规定的过流保护门限,RCS是与ISENx脚相连的电流感应电阻。如果过流持续2个时钟周期,则进入Hiccup模式,门驱动器断开,进入软启动。重新启动前,IC在软启动过程中要循环两次。IC会在软启动过程中持续循环,直到过流现象消除为止。

图3中SYNC脚用来实现两个或多个ISL6443控制器的同步。使用时需接下拉电阻,不用时将其与VCC_5V相连。

2.2 PCB布局考虑

布局对基于ISL6443的DC-DC转换器的成功实现非常关键。ISL6443工作在高频模式下,开关时间非常短,在这种开关频率下,即使最短的连线也会产生较大的阻抗。同时,峰值门驱动电流也会在极短的时间内显著升高。电流从一个器件到另一器件的转换速度引起互连阻抗和寄生电路元件上的电压尖脉冲。该电压尖脉冲会降低效率,产生EMI,增加过压应力和阻尼振荡。仔细考虑PCB板布局,可使电压尖脉冲的值最小。针对以上考虑总结了几点布局上需注意的地方[4]:

(1)输入电容、高端FET、低端FET、电感和输出电容应首先放置。将输入高频去耦电容放在非常靠近MOSFET的地方。

(2)在IC附近建立一个小的模拟接地平面。将SGND脚接至该平面,包括反馈电阻、电流极限设置电阻以及SDx下拉电阻的所有小信号接地端都接至SGND平面。

(3)高电流接地端PGND与小信号接地端SGND必须分开,在靠近IC的地方将SGND和PGND相连。

(4)确保从输入电容到MOSFET、输出电感和输出电容的电流通路尽可能短,同时有最大的容许线宽。

(5)将PWM控制器靠近低端FET 放置。LGATE 的连接应该较短而且较宽。IC最好放置在无噪声接地的地方。

(6)将VCC_5V旁路电容接在非常靠近VCC_5V脚的地方,将它的接地端接至PGND上。将门驱动元件自举二极管和自举电容放在接近IC的地方。

(7)输出电容应尽量靠近负载。用短而宽的覆铜层连接输出电容和负载,避免产生感抗和阻抗。

3 实验数据分析与验证

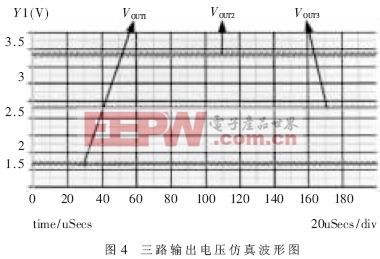

利用Catena公司提供的SIMetrix/SIMPLIS仿真工具实现了该电源方案的分析和验证,具体方法可查阅参考文献[6][7][8]。

图4所示为ISL6443三路输出电压波形,PWM控制器门驱动器的电压上升和下降时间均为18ns左右。因此,三路输出电压能在极短的时间内达到稳定值,从而满足了FPGA的性能要求。

图5所示为两个PWM控制器的输出波形。图中可以看出,ISL6443的两个PWM控制器呈180°异相工作,以减小输入纹波电流。这降低了对输入电容纹波电流的要求,减小了电源的感生噪声,同时也提高了EMI抗干扰性能。

图6所示为ISL6443软启动仿真波形。软启动功能使转换器的输出被监控,得到过载、短路和欠压保护。输出持续过载会使PGOOD置低,从而进入软启动模式,直到过载现象消除为止。

本文利用Intersil高效三输出同步补偿稳定器实现了StratixTM FPGA的电源系统设计,并且进行了一系列的仿真分析与验证实验。实验表明该设计方案合理有效,易于实现,有较好的参考价值和实用价值。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)